### A Survey of Time and Space Partitioning for Space Avionics

Jan Bredereke

City University of Applied Sciences Bremen

Flughafenallee 10, 28199 Bremen, Germany jan.bredereke@hs-bremen.de

Technical Report

Version: 1.1

### **Document Version History**

| Version | Date         | Changes                                                                 |

|---------|--------------|-------------------------------------------------------------------------|

| 1.1     | 16 Feb. 2017 | made file format PDF/A compliant (mostly)                               |

|         |              | p. iii: added "Keywords:" section                                       |

|         |              | Corrected typos: p. 25: "partiti[o]ning", p. 29: "Component<br>Base[d]" |

| 1.0     | 27 June 2016 | Initial version.                                                        |

#### Abstract

We present a survey of the current state of the reseach on time and space partitioning for space avionics. The availability of ever more powerful computers allows to assign many control tasks to a single computer easily, in principle. But in its naïve form, this would mean too much effort and thus cost for demonstrating dependability. For aircraft, there is already an approach to solve this problem, the Integrated Modular Avionics (IMA) architecture. For spacecraft, the basic problem is similar. But in detail, the setting is different, though. This report compiles a survey and identifies relevant research challenges. Based on some of them, we propose to design a multi-core processor architecture that avoids fundamental problems of the current architectures with respect to time partitioning, and that can be used in the space domain.

Keywords: time and space partitioning, space avionics, integrated modular avionics

## Contents

| 1 | Intro                                          | Introduction                                                       |    |  |  |  |

|---|------------------------------------------------|--------------------------------------------------------------------|----|--|--|--|

| 2 | Syst                                           | ems with Mixed Dependability                                       | 2  |  |  |  |

|   | 2.1                                            | Dependability                                                      | 2  |  |  |  |

|   | 2.2                                            | Mixed Dependability                                                | 2  |  |  |  |

|   | 2.3                                            | Handling Mixed Dependability                                       | 3  |  |  |  |

|   |                                                | 2.3.1 Separation Kernel                                            | 3  |  |  |  |

|   |                                                | 2.3.2 Virtualization                                               | 3  |  |  |  |

|   |                                                | 2.3.3 Separation Kernel vs. Virtualization                         | 4  |  |  |  |

| 3 | Timing Analysis                                |                                                                    |    |  |  |  |

|   | 3.1                                            | Proof Techniques for Real-Time Properties                          | 5  |  |  |  |

|   | 3.2                                            | Trends in Processor Architecture with Relevance to Timing Analysis | 6  |  |  |  |

| 4 | Integrated Modular Avionics (IMA) for Aircraft |                                                                    |    |  |  |  |

|   | 4.1                                            | From a Federated Architecture to the IMA Architecture              | 8  |  |  |  |

|   | 4.2                                            | AFDX Data Network                                                  | 9  |  |  |  |

|   | 4.3                                            | Operating System Interface ARINC 653                               | 10 |  |  |  |

|   | 4.4                                            | Distributed Modular Electronics (DME)                              | 11 |  |  |  |

| 5 | Diff                                           | erences between the Aeronautical and the Space Domain              | 13 |  |  |  |

|   | 5.1                                            | The Speed of Growth of Complexity                                  | 13 |  |  |  |

|   | 5.2                                            | Scale of Communication Demands                                     | 14 |  |  |  |

|   | 5.3                                            | Online/Offline Maintenance                                         | 14 |  |  |  |

|   | 5.4                                            | Pronounced Mission Phases                                          | 14 |  |  |  |

|   | 5.5                                            | Availability of a Hardware-Based Memory Protection Unit            | 15 |  |  |  |

|   | 5.6                                            | Radiation                                                          | 15 |  |  |  |

|   | 5.7                                            | Miscellaneous: Differences Between Launchers and Satellites        | 15 |  |  |  |

| 6 | Existing Work on Time and Space Partitioning Suitable for Space Avionics |                                                                                                       |                                                                                         | 16       |  |  |

|---|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------|--|--|

|   | 6.1                                                                      | The IN                                                                                                | IA-SP Project: an Adaption of IMA for Space Avionics                                    | 16       |  |  |

|   |                                                                          | 6.1.1                                                                                                 | The Original IMA-SP Project                                                             | 16       |  |  |

|   |                                                                          | 6.1.2                                                                                                 | Follow-Up Assessment Study on Partitioning and Maintenance of Flight Software in IMA-SP | 19       |  |  |

|   |                                                                          | 6.1.3                                                                                                 | The IMA-SP System Design Toolkit Project                                                | 19       |  |  |

|   | 6.2                                                                      | The S/                                                                                                | AVOIR-IMA Initiative: A TSP Based Software Reference Architecture                       | 20       |  |  |

|   | 6.3                                                                      | Virtua                                                                                                | lization Solutions Suitable for Space Avionics                                          | 21       |  |  |

|   |                                                                          | 6.3.1                                                                                                 | XtratuM: a Hypervisor for Safety-Critical Embedded Systems                              | 21       |  |  |

|   |                                                                          | 6.3.2                                                                                                 | Our Case Study Using XtratuM for a Portable Real-Time Application                       | 23       |  |  |

|   |                                                                          | 6.3.3                                                                                                 | The MultiPARTES Project: an Extension of XtratuM for Multi-Core Pro-<br>cessors         | 24       |  |  |

|   |                                                                          | 6.3.4                                                                                                 | AIR: A Partition Management Kernel Based on RTEMS                                       | 24       |  |  |

|   | 6.4                                                                      | Separa                                                                                                | tion Kernels Suitable for Space Avionics                                                | 27       |  |  |

|   |                                                                          | 6.4.1                                                                                                 | PikeOS                                                                                  | 27       |  |  |

|   |                                                                          | 6.4.2                                                                                                 | VxWorks 653                                                                             | 28       |  |  |

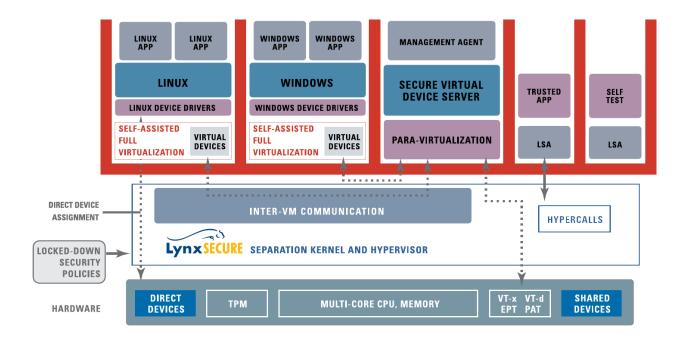

|   |                                                                          | 6.4.3                                                                                                 | LynxSecure                                                                              | 29       |  |  |

|   |                                                                          | 6.4.4                                                                                                 | РОК                                                                                     | 29       |  |  |

|   | 6.5                                                                      | Compo                                                                                                 | onent Based Software Architectures                                                      | 29       |  |  |

| 7 | Rese                                                                     | Research Challenges                                                                                   |                                                                                         |          |  |  |

|   | 7.1                                                                      | CPU-F                                                                                                 | Related Challenges for Time Partitioning                                                | 30       |  |  |

|   |                                                                          | 7.1.1                                                                                                 | Multi-Core CPUs                                                                         | 30       |  |  |

|   |                                                                          | 7.1.2                                                                                                 | Direct Memory Access (DMA)                                                              | 31       |  |  |

|   | 7.2                                                                      | Challenges for Real-Time Property Proofs                                                              |                                                                                         | 31       |  |  |

|   |                                                                          | 7.2.1                                                                                                 | Processor Architecture                                                                  | 31       |  |  |

|   |                                                                          | 7.2.2                                                                                                 | Virtualization                                                                          | 32       |  |  |

|   |                                                                          | 7.2.3                                                                                                 | Distributed Computing                                                                   | 32       |  |  |

|   | 7.3                                                                      | Separa                                                                                                | tion Kernel vs. Virtualization for TSP                                                  | 33       |  |  |

|   | 7.4                                                                      | Identification of the Common Properties of the Aeronautical and the Space DomainWith Respect to TSP33 |                                                                                         |          |  |  |

|   | 7.5                                                                      | Adaption of IMA-SP to Launchers                                                                       |                                                                                         |          |  |  |

|   | 7.6                                                                      | An Existing Survey on Research Challenges for Mixed-Criticality Systems 3                             |                                                                                         |          |  |  |

|   | 7.7                                                                      | Probat                                                                                                | bly Not: Hierarchical Scheduling for Mixed-Criticality Systems                          | 34       |  |  |

| 8 | Idea                                                                     | : A Pr                                                                                                | ocessor Architecture for Time Partitioning in the Space Domain                          | 35       |  |  |

|   |                                                                          |                                                                                                       |                                                                                         |          |  |  |

|   | 8.1                                                                      | The P                                                                                                 | roposed Processor Architecture                                                          | 35       |  |  |

|   | 8.1<br>8.2                                                               |                                                                                                       | roposed Processor Architecture                                                          | 35<br>35 |  |  |

|    | 8.4          | Discussion of the Approach |                                                                        |    |

|----|--------------|----------------------------|------------------------------------------------------------------------|----|

|    | 8.5          | Related Research           |                                                                        | 37 |

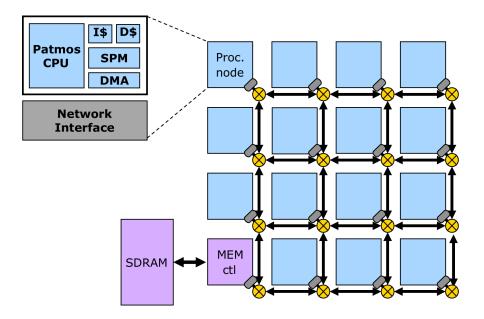

|    |              | 8.5.1                      | Non-Mainstream Trends in Processor Architecture                        | 37 |

|    |              | 8.5.2                      | The T-CREST Project: a Time-Predictable Multi-Core Architecture        | 37 |

| 9  |              | ch of<br>surem             | an Idea: a Processor Architecture Specifically Supporting WCET<br>ents | 39 |

| 10 | 10 Summary   |                            |                                                                        | 40 |

| Bi | Bibliography |                            |                                                                        | 42 |

Chapter

### Introduction

We present a survey of the current state of the reseach on time and space partitioning for space avionics. Avionics is the set of electronic systems, in particular computers, on board of an aircraft or spacecraft. Such systems must be dependable. There are significantly different levels of dependability, for example for the cabin electronics of an aircraft and for its autopilot. The higher the level required, the higher the effort necessary for demonstrating dependability. The traditional approach therefore provisions separate computer hardware for each control task. The effort for demonstrating dependability then follows from the level targeted, for each task.

The availability of ever more powerful computers allows to assign many control tasks to a single computer easily, in principle. This would have the advantage of saving considerable weight and thus cost for the aircraft or spacecraft. But this idea, in its naïve form, would mean too much effort and thus cost for demonstrating dependability. A level demanded by one of the tasks must be applied to all of them.

For aircraft, there is an approach for this already. The Integrated Modular Avionics (IMA) architecture (see Chap. 4 below) is a software and hardware platform which isolates software programs from each other. The dependability needs to be demonstrated at the highest level only once, for the platform. This concept is used in practice already for the aircraft Airbus A380, Airbus A400M, and Boeing 787 Dreamliner.

For spacecraft, the basic problem is similar. We want to run several tasks on a single computer (or a few computers) for cost reasons, with dependability requirements that are high, too. But in detail, the setting is different, though. There is already some research on time and space partitioning of control tasks in space craft. But there is not yet a concept proven in practice.

Further domains have similar problems and according solution approaches. In the automotive domain, the AutoSAR initiative (automotive open system architecture) is related. We do not survey it here since it is not as practice proven yet as IMA in the avionics domain, and since our research resources are limited.

The aim of this work is to compile a survey and to identify relevant research challenges. We hope to then pursue some of these research questions further. Our work here was conducted during a (partial) sabbatical in winter term 2015/16 and during the following summer term 2016.

We thank the people at the Data Handling Avionics department of Airbus DS, Bremen, for pointing us at this interesting research subject.

## Systems with Mixed Dependability

In this chapter, we introduce to systems with mixed dependability. We briefly introduce to the notions of dependability and of mixed dependability first. We then describe two mechanisms to handle mixed dependability.

### 2.1 Dependability

The survey paper by Avižienis *et. al.* [Avi+04] provides definitions for dependability in the domains of computing and communication systems. The original definition of dependability is the ability to deliver service that can be justifiably trusted. This definition stresses the need for justification of trust. The alternate definition that provides the criterion for deciding if the service is dependable is: the dependability of a system is the ability to avoid service failures that are more frequent and more severe than is acceptable.

Dependability is an integrating concept that encompasses the following attributes [Avi+04]:

availability: readiness for correct service.

reliability: continuity of correct service.

safety: absence of catastrophic consequences on the user(s) and the environment.

integrity: absence of improper system alterations.

maintainability: ability to undergo modifications and repairs.

### 2.2 Mixed Dependability

A system with mixed dependability is a system where components with different dependability levels coexist on the same execution platform. Crespo *et. al.* [Cre+14] call this a "mixed criticality system" (MCS): Increasing processing power makes it possible to integrate more and more components on a single execution platform. However, if at least some of the components must be dependable, adequate validation (and often certification) is necessary, such that validation costs can become prohibitive for further integration. This trend can be observed in many different domains. Examples are the aeronautical domain, the space domain, the automotive domain, and industry automation.

### 2.3 Handling Mixed Dependability

A general approach to this is to separate the components on the single execution platform so well that only the separation mechanism and the high dependability components need to be validated for a high dependability. Mechanisms to achieve such a separation comprise a *separation kernel* and *virtualization*.

### 2.3.1 Separation Kernel

A separation kernel is a combination of hardware and software for allowing multiple functions to be performed on a common set of physical resources without interference [Cre+14]. It was first proposed by Rushby [Rus81], aiming at security problems.

According to Crespo *et. al.* [Cre+14], the MILS architecture, developed by the MILS (Multiple Independent Levels of Security and Safety) initiative [Alv+05], is a separation kernel. In addition, the ARINC-653 standard [Aer05] uses these principles to define a baseline operating environment for application software used within Integrated Modular Avionics (IMA), based on a partitioned architecture. Wie will describe IMA in more detail in Chap. 4.

### 2.3.2 Virtualization

Crespo *et. al.* [Cre+14] use virtualization as a separation mechanism. A hypervisor implements partitions or virtual machines that are isolated from each other in the temporal and spatial (i.e., storage) domains.

Different kinds of isolation must be considered [Cre+14, Sect. 2.1]:

Fault isolation: a fault in an application must not propagate to other applications.

**Spatial isolation:** applications must execute in independent physical memory address spaces.

**Temporal isolation:** the real-time behaviour of an application must be correct independent of the execution of other applications.

Crespo *et. al.* [Cre+14, Sect. 2.1] propose a predefined and static allocation of resources to partitions, in order to achieve a separation that is sufficiently simple to allow for separate validation. The resources comprise CPU time, memory areas, IO ports, etc. Static allocation of CPU time should be achieved by a cyclic scheduling policy for partition execution.

Crespo et. al. [Cre+14, Sect. 3] state that there is some confusion of terminology on virtualization, and they propose the following definitions: A *type 1 hypervisor* (also named native or bare-metal hypervisor) runs directly on the native hardware, while a *type 2 hypervisor* is executed on top of an operating system. *Full virtualization* provides a complete re-creation of the hardware behaviour of a native system to a guest system, while *para-virtualization* requires the guest system to be modified: Some machine instructions are replaced by functions provided by the hypervisor. In full virtualization, certain "conflicting" machine instructions must be caught during runtime, in order to maintain the spatial and temporal separation. They are then handled by the hypervisor. With para-virtualization, in contrast, no catching is necessary, and the handling can use more information from the guest. This improves the performance greatly, and it simplifies the hypervisor. Of course, the source code of the guest must be available for recompiling. Since the latter usually is not a problem for mixed dependability systems, para-virtualization is preferable here.

Crespo *et. al.* [Cre+14, Sect. 3.2] categorize the IMA architecture (see Chap. 4 below) as a separation kernel. However, part of it comes close to the functionality provided by a hypervisor.

Conceived by the same research group, XtratuM (see Sect. 6.3.1) is an open-source, type 1 hypervisor that uses para-virtualization. It was designed specifically for mixed-criticality systems.

Virtualization aims at presenting a virtual machine to an application software which is exactly like the real machine. However, it cannot hide one kind of difference: the machine instructions are not executed evenly in the time sense anymore. There are "holes" where other partitions get time. The application software can notice this when it interacts with the system's environment. This is relevant for real-time applications, for example for control applications where the controlled system does not stop while the application is on hold. Another example is the interaction with peripheral devices which change state by progress of time, such as timers.

The latency of an interrupt can become substantially higher, i.e., until the partition of the interrupt is scheduled again. This can break assumptions about the timing of interrupts made by an application or by an operating system. For example, Ripoll *et. al.* [Rip+10, Sect. 3.2] report that they used the RTEMS operating system in a partition, and that the timer tick of the RTEMS operating system was faster than the schedule period of the partition. Therefore, they had to take measures to ensure that accumulated clock ticks were presented to the partition at the beginning of its time slot.

### 2.3.3 Separation Kernel vs. Virtualization

Separation is a solution to the problem of mixed dependability, and virtualization is one possible mechanism to achive separation. Virtualization comprises more than necessary to achive separation. For example, the application in a (fully) virtualized machine cannot "see" any differences (besides "holes in time") to a dedicated real machine. This is not necessary for separation. Instead, we can provide some modification of a real machine to the application, as long as it guarantees separation. The approach of para-virtualization (compare Sect. 2.3.2 above) goes a step into exactly this direction.

A separation kernel imposes the use of the same operating system onto all applications, while virtualization allows for different operating systems (or even bare-metal applications without any operating system) in its partitions. The latter can be a substantial advantage if heterogeneous applications are to be integrated.

A separation kernel usually comprises more functionality (e.g., on communication, and maybe on multi-threading) than a hypervisor used for virtualization. Therefore, we suspect that the effort necessary for verifying the time and space separation property is usually higher for a separation kernel.

See also Sect. 7.3 on the research challenge on which of the two mechanisms has which relative pros and cons, under which conditions.

# Chapter

# Timing Analysis

This chapter provides some basic knowledge on timing analysis. We need this knowledge for further discussions of time partitioning and, later on, for an idea on a processor architecture supporting time partitioning.

### 3.1 Proof Techniques for Real-Time Properties

In this section, we introduce to proof techniques for real-time properties of embedded systems such as space avionics. This provides the background for the discussion of time partitioning further below. Embedded systems such as space avionics often must satisfy hard real-time properties. That is, they provably must provide the reaction to a stimulus before a given limit of time. Techniques exist to provide such proofs. The worst-case execution time (WCET) is the maximum time a piece of code will ever need for execution on a given hardware, regardless of input and internal state. The proof of a hard real-time property consists in establishing an upper bound for the WCET which does not exceed the given limit. Usually an upper bound is used, instead of the actual WCET, because of a lack of more precise information. This information has been abstracted away in order to reduce the effort of analysis (or to make it feasible in the first place).

In a partitioned system, there is an execution time budget for each partition. Accordingly, the proofs of the hard real-time properties of all partitions must be carried out, hopefully in a (mostly) independent way.

Kopetz [Kop11, p. 245] describes how to determine an upper bound for the execution time of machine code commands on a target hardware. If the processor of the target hardware has fixed instruction execution times, the duration of the hardware instructions can be found in the hardware documentation and can be retrieved by an elementary table look-up. The adding-up of the instruction execution times must be done for all combinations of input and initial state. Such a simple approach does not work if the target hardware is a modern RISC processor with pipelined execution units and instruction/data caches. While these architectural features result in significant performance improvements, they also introduce a high level of unpredictability. Dependencies among instruction execution. To make things worse, these two effects are not independent. A significant amount of research deals with the execution time analysis on machines with pipelines and caches. The excellent survey article by Wilhelm *et. al.* [Wil+08] presents the state of the art of execution time bounds analysis in research and industry in depth, and it describes many of the tools available for the support of execution time bounds analysis.

A book chapter by Wilhelm [Wil09] elaborates even further on how to determine bounds on execution times.

Wilhelm *et. al.* [Wil+08, Chap. 2.1.3] point out the problem of timing anomalies. A timing anomaly is a counterintuitive influence of the (local) execution time of one machine instruction on the (global) execution time of the whole task. For example, a cache miss may speed up the global execution, instead of slowing it down, if it prevents a more expensive branch misprediction. Besides such speculation-caused anomalies, there also can be instances of the well-known scheduling anomalies. One consequence of these anomalies is that no worst case initial execution state exists. For example, an initially empty cache may not be the worst case. This prevents safe timing measurements on isolated snippets of code. All this holds if and only if the processor architecture is sufficiently complex for timing anomalies to occur. It usually does not hold for simpler 8- and 16-bit processors.

Kopetz [Kop11, p. 247] continues to describe the state of practice in determining a reasonable upper bound for the WCET of a task. It includes the use of a restricted architecture that reduces the interactions among the tasks and the extensive testing of the complete implementation. He finishes that the state of current practice is not satisfactory. We add that Wilhelm *et. al.* [Wil+08] have presented satisfactory methods and tools; they are just not yet the general state of practice.

Cooling [Coo03, Chap. 14] surveys methods for performance engineering for real-time systems. That is, which design management approaches can help to achieve a desired performance.

### 3.2 Trends in Processor Architecture with Relevance to Timing Analysis

Wilhelm *et. al.* [Wil+08, Sect. 11.2] summarize current trends in processor architecture which are relevant to timing analysis:

"The hardware used in creating an embedded real-time system has a great effect on the ease of predictability of the execution time of programs.

The simplest case are traditional 8- and 16-bit processors with simple architectures. In such processors, each instruction basically has a fixed execution time. Such processors are easy to model from the hardware timing perspective, and the only significant problem in WCET analysis is how to determine the program flow.

There is also a class of processors with simple in-order pipelines, which are found in cost-sensitive applications requiring higher performance than that offered by classic 8- and 16-bit processors. Examples are the ARM7 and the recent ARM Cortex R series. Over time, these chips can be expected to replace the 8- and 16-bit processors for most applications. With their typically simple pipelines and cache structures, relatively simple and fast WCET hardware analysis methods can be applied.

At the high end of the embedded real-time spectrum, performance requirements for applications, like flight control and engine control, force real-time systems designers to use complex processors with caches and out-of-order execution. Examples are the PowerPC 750, PowerPC 7448, and ARM11 families of processors. Analyzing such processors requires more advanced tools and methods, especially in the hardware analysis.

The mainstream of computer architecture is steadily adding complexity and speculative features in order to push the performance envelope.  $[\dots]$  This mainstream trend of ever-more complex processors is no longer as dominant as it used to be, however. In recent years, several other design

alternatives have emerged in the mainstream, where the complexity of individual processor cores has been reduced significantly.

Many new processors are designed by using several simple cores instead of a single or a few complex cores. This design gains throughput per chip by running more tasks in parallel, at the expense of single-task performance. Examples are the Sun Niagara chip, which combines eight in-order four-way multithreaded cores on a single chip [OH05] and the IBM-designed PowerPC for the Xbox 360, using three two-way multithreaded in-order cores [Kre05]. These designs are cache-coherent multiprocessors on a chip and thus have a fairly complex cache and memory system. The complexity of analysis moves from the behavior of the individual cores to the interplay between them as they access memory.

Another very relevant design alternative is to use several simple processors with private memories (instead of shared memory). This design is common in mobile phones, where you typically find an ARM main processor combined with one or more DSPs on a single chip. Outside the mobile phone industry, the IBM–Sony-Toshiba Cell processor is a high-profile design using a simple in-order PowerPC core along with eight synergistic processing elements (SPEs) [Hof05]. The Cell will make its first appearance in the Sony PlayStation 3 gaming console, but IBM and Mercury Computing systems are pushing the Cell as a general-purpose real-time processor for high-performance real-time systems. The SPEs in the Cell are designed for predictable performance and use local program-controlled memories rather than caches, just like most DSPs. Thus, this type of architecture provides several easy-to-predict processors on a chip as an alternative to a single hard-to-predict processor.

Field-programmable gate arrays (FPGAs) are another design alternative for some embedded applications. Several processor architectures are available as "soft cores" that can be implemented in an FPGA together with application-specific logic and interfaces. Such processor implementations may have application-specific timing behavior, which may be challenging for off-the-shelf timing analysis tools, but they are also likely to be less complex and thus easier to analyze than general-purpose processors of similar size. Likewise, some standard processors are now packaged together with FPGA on the same chip for implementing application-specific logic functions. [...]

There is also work on application-specific processors or application-specific extensions to standard instruction sets, again creating challenges for timing analysis.  $[\dots]$ "

# Integrated Modular Avionics (IMA) for Aircraft

In this chapter, we give an overview of the Integrated Modular Avionics (IMA) architecture which is used for aircraft. We describe why it was developed, and which are the key properties of its constituent data network and of its operating system interface. Furthermore, we outline the extension to Distributed Modular Electronics (DME).

Our overview draws on the well-written background chapter of the recent dissertation thesis of Efkemann [Efk14, Chap. 2]. A good source for further reading is Ott [Ott07]. She gives a broad view on both architectures and development processes, and there in particular on testing processes.

### 4.1 From a Federated Architecture to the IMA Architecture

Efkemann [Efk14, Chap. 2] presents the following overview of Integrated Modular Avionics (IMA) in his dissertation thesis:

"The traditional *federated* aircraft controller architecture [Fil03, p. 4] consists of a large number of different, specialised electronics devices. Each of them is dedicated to a special, singular purpose (e. g. flight control, or fire and smoke detection) and has its own custom sensor/actuator wiring. Some of them are linked to each other with dedicated data connections. In the *Integrated Modular Avionics* (IMA) architecture this multitude of device types is replaced by a small number of modular, general-purpose component variants whose instances are linked by a high-speed data network. Due to high processing power each module can host several avionics functions, each of which previously required its own controller. The IMA approach has several main advantages:

- Reduction of weight through a smaller number of physical components and reduced wiring, thereby increasing fuel efficiency.

- Reduction of on-board power consumption by more effective use of computing power and electrical components.

- Lower maintenance costs by reducing the number of different types of replacement units needed to keep on stock.

- Reduction of development costs by provision of a standardised operating system, together with standardised drivers for the avionics interfaces most widely used.

• Reduction of certification effort and costs via incremental certification of hard- and software.

An important aspect of module design is *segregation*: In order to host applications of different safety assurance levels on the same module, it must be ensured that those applications cannot interfere with each other. Therefore a module must support resource partitioning via memory access protection, strict deterministic scheduling and I/O access permissions. Bandwidth limitations on the data network have to be enforced as well.

The standard aircraft documentation reference for IMA is ATA chapter 42. The IMA architecture is currently in use in the Airbus A380, A400M, the future A350XWB, and Boeing 787 Dreamliner aircraft. Predecessors of this architecture can be found in so-called fourth-generation jet fighter aircraft like the Dassault Rafale."

### 4.2 AFDX Data Network

Efkemann [Efk14, Chap. 2.1] continues with an overview of the AFDX data network employed by the IMA architecture:

"A data network is required for communication between (redundant) IMA modules as well as other hardware. This role is fulfilled by the *Avionics Full DupleX Switched Ethernet* (AFDX) network. It is an implementation of the ARINC specification 664 [Aer09] and is used as high-speed communication link between aircraft controllers. It is the successor of the slower ARINC 429 networks [Aer04].

AFDX is based on 100 Mbit/s Ethernet over twisted-pair copper wires (IEEE 802.3u, 100BASE-TX). This means it is compatible with COTS Ethernet equipment on layers 1 and 2 (physical layer and link layer). Ethernet by itself is not suitable for real-time applications as its timing is not deterministic. Therefore AFDX imposes some constraints in order to achieve full determinism and hard real-time capability.

In AFDX, so called *Virtual Links* (VLs) are employed for bandwidth allocation and packet routing. Each VL has a 16-bit ID, which is encoded into the destination MAC address of each frame sent through this VL. For each VL, only one end system can send frames, while there can be one or more receivers (unidirectional multicast communication, similar to ARINC 429). AFDX switches use a pre-determined configuration to deliver frames based on their VL ID to a set of receiving end systems.

Each VL is allocated a part of the full bandwidth of an AFDX link. To that end, each VL has two attributes: a maximum frame length  $(L_{max})$  in bytes and a bandwidth allocation gap (BAG). The BAG value represents the minimum interval (in milliseconds) between two frames on that VL. Thus, the maximum usable bandwidth in bit/s of a VL can be calculated as:

$$b_{\max} = L_{\max} \cdot 8 \cdot 1000 / \mathsf{BAG}$$

End systems use a VL scheduler to ensure minimum latency and jitter for each VL.

[...]

In order to increase reliability, an aircraft data network consists of two independent switched networks. AFDX frames are sent on both networks. If no frame is lost, the other end systems will receive two frames. In order to identify matching frames sent over the redundant links, the message payload is followed by a sequence number field. Of two frames received on different networks with an identical sequence number, only the first is passed up the protocol stack."

Ott [Ott07, Chap. 1.6.3] provides a substantially more detailed overview of AFDX.

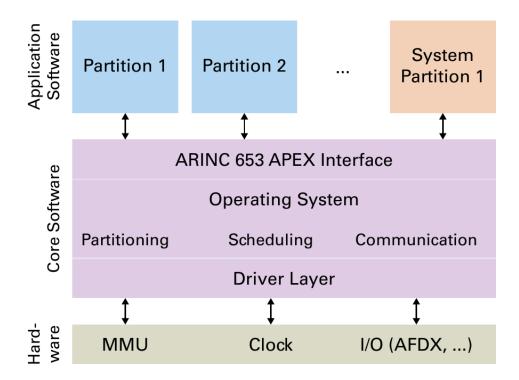

Figure 4.1: IMA module system architecture (taken from [Efk14, Fig. 2.2])

### 4.3 Operating System Interface ARINC 653

Efkemann [Efk14, Chap. 2.2] then introduces to the operating system interface ARINC 653 of the IMA architecture:

"[...], an IMA module can host multiple avionics functions. The interface between avionics applications and the module's operating system conforms to a standardised API which is defined in the ARINC specification 653 [Aer05].

The system architecture of an IMA module is depicted in figure 4.1. A real-time operating system kernel constitutes the central component. It uses a driver layer for access to the module's I/O hardware (either solely AFDX, or other interfaces like Discretes, CAN, and ARINC 429 buses as well, depending on module type) [Aer05, p. 11]."

Efkemann [Efk14, Chap. 2.2.1] details the partitioning as follows:

"In order to guarantee the same isolation of avionics functions residing on a shared module as a federated architecture would provide, it is the operating system's responsibility to implement a concept called *partitioning*. According to [RTC01], a partitioning implementation should comply with the following requirements:

- A software partition should not be allowed to contaminate another partition's code, I/O, or data storage areas.

- A software partition should be allowed to consume shared processor resources only during its period of execution.

- A software partition should be allowed to consume shared I/O resources only during its period of execution.

- Failures of hardware unique to a software partition should not cause adverse effects on other software partitions.

• Software providing partitioning should have the same or higher software level<sup>1</sup> than the highest level of the partitioned software applications.

On the IMA platform, a partition is a fixed set of the module's resources to be used by an avionics application. In particular, each partition is assigned a portion of the module's memory. The operating system ensures that other partitions can neither modify nor access the memory of a partition, similar to memory protection in a UNIX-like operating system. Each partition also receives a fixed amount of CPU time. The operating system's scheduler ensures that no partition can spend CPU time allotted to another partition [Aer05, p. 13].

Two kinds of partitions reside on a module:

- **Application partitions** contain application code that makes up (part of) the implementation of an avionics function.

- **System partitions** on the other hand provide additional module-related services like data loading or health monitoring.

Inside a partition there can be multiple threads of execution, called *processes*. Similar to POSIX threads, all processes within a partition share the resources allocated to the partition. Each process has a priority. A process with a higher priority pre-empts any processes with a lower priority. ARINC 653 defines a set of states a process can be in (Dormant, Waiting, Ready, Running) as well as API functions for process creation and management [Aer05, p. 18–25]."

In the following, Efkemann [Efk14, Chap. 2.2.2] discusses the methods of communication in length. A brief summary is:

"The operating system must provide a set of different methods of communication. All of them fall into either of two categories: intra-partition or interpartition communication. Intra-partition communication always happens between processes of the same partition, while inter-partition communication happens between processes of different partitions or even partitions on different modules. [...]"

### 4.4 Distributed Modular Electronics (DME)

Distributed Modular Electronics (DME) is an extension of the IMA concept. It was developed in the SCARLETT research project (SCAlable & ReconfigurabLe elEctronics plaTforms and Tool). SCARLETT was a joint European research and technology project of airframers, large industrial companies, SMEs, and universities [SCA13].

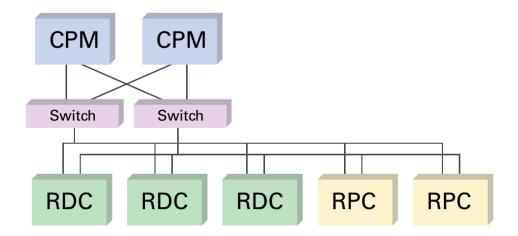

According to Efkemann [Efk14, Chap. 2.5], "the DME concept aims at the separation of processing power from sensor/actuator interfaces, thereby reducing the number of different component types to a minimum. This also makes DME suitable for a wider range of aircraft types by giving system designers the possibility to scale the platform according to required hardware interfaces and computing power. Figure 4.2 shows an example of a network of components: two Core Processing Modules (CPM), three Remote Data Concentrators (RDC), and two Remote Power Controllers (RPC) linked via two redundant AFDX networks. The CPM components provide the computing power and host the avionics applications, but apart from AFDX they do not provide any I/O hardware interfaces. Instead, the RDC and RPC components provide the required number of sensor/actuator and bus interfaces.

<sup>&</sup>lt;sup>1</sup>as defined in [RTC92]

Figure 4.2: Distributed Modular Electronics (DME) architecture (taken from [Efk14, Fig. 2.3])

The project also investigates ways of increasing fault tolerance through different reconfiguration capabilities, for example transferring avionics functions from defective modules to other, still operative modules. Finally, the design of a unified tool chain and development environment has led to improvements of the avionics software implementation process. [...]"

# Chapter

# Differences between the Aeronautical and the Space Domain

There are significant differences between the aeronautical and the space domain, with respect to time and space partitioning.

### 5.1 The Speed of Growth of Complexity

Windsor and Hjortnaes [WH09, Sec. IV.B] state that the space domain mastered integrating applications on a single CPU earlier than the aeronautical domain. This was achieved by validating everything at the highest integrity level. But this now becomes more and more expensive due to the increasing complexity of mission applications. The Central Flight Software (CFS) encompasses the Data Management (DMS) and the Attitude & Orbital Control (AOCS) functional chains. Recently, they are integrated on one computer instead of independent computers linked by a data bus ([WH09, Sec. V.A]). Similarly, the payload software consists of several components of differing criticality: command and control has a higher criticality than payload data processing. These payload functions co-exist on one or several on-board computers (OBCs) and are under the responsibility of one or several organizations ([WH09, Sec. V.B]).

The complexity problems hit the space domain later than the aeronautical domain. We suppose the reason is that the space domain must use slower and therefore less powerful computers due to the harsh radiation environment in space (compare Sect. 5.6 below). Therefore, the space domain only recently reached the critical region of complexity.

Windsor *et. al.* [WDD11] provide some concrete numbers on complexity for the Airbus A380: its IMA platform is composed of up to 30 IMA modules of 8 different types, hosting 21 avionics functions which were developed by 10 function suppliers. In contrast, the IMA-SP architecture envisioned by Windsor *et. al.* will have less computing nodes (e.g., central on board computer, payload computer, and intelligent sensors and actuators), connected to a less powerful network based on SpaceWire or MIL-STD-1553B), and hosting fewer functions developed by small numbers of suppliers.

### 5.2 Scale of Communication Demands

The space domain appears to have significantly smaller demands on communication. Even though the International Space Station (ISS) features a complexity similar to that of an airplane, a typical satellite or launcher is much simpler; compare the end of the previous section. Accordingly, only a few hardware nodes need to be connected, with less bandwith. Windsor *et. al.* [WDD11] even explicitly consider the communication bus optional for the IMA-SP platform, for the case of a single hardware node. We add that the necessary redundancy against hardware failures nevertheless demands at least two hardware nodes. Depending on the redundancy concept, there might be little demand for them to communicate, however.

### 5.3 Online/Offline Maintenance

All aeronautical software maintenance is performed off-line, while the aircraft ist at the ground safely. In contrast, spacecraft operations require the system to be active ([WH09, Sec. VI.B].

Usually, a spacecraft is launched with the complete mission definition implemented in the flight software, from a pre-launch support mode to payload operations phase [WH09, Sect. V.D]. However, there is interest for adding new applications to extend the mission. This has been done in a few cases, but with extensive validation effort. And in the commercial satellite market, operators would like to have the in-flight capability to safely upload private payload applications to their spacecraft without the involvement of the manufacturer.

We add that the redundancy of multiple computer hardware may be used to take one of the computers offline in order to install a new software version. But this can be done for a short period of time only. And the new software version must be already validated fully. We have devised such an update process for the first in-space flight software update of the main computers of the European Columbus module which is part of the International Space Station [Bre08].

The IMA concept of the aeronautical domain requires substantial offline effort for reconfiguring communication paths. The virtual links (VLs) of the AFDX network are static. When the network routing shall be changed, each node affected must be accessed by a technician in order to apply this software update. This approach of IMA cannot be applied in the space domain, where physical access is impossible in nearly all cases.

### 5.4 Pronounced Mission Phases

Satellites have more pronounced mission phases than aircraft. Aircraft operate in different modes on ground, during ascent, cruise, and decent. Switches between these modes can occur rapidly. Long-lived satellites have longer-lasting and more predictable mission phases, such as ascent, orbit insertion, orbital payload operation, and deorbiting.

This offers the opportunity to reconfigure the computing resources between mission phases. At least, no computing time needs to be allocated to functions not active in the current mission phase. Since there is plenty of time after orbit insertion, the software even could be updated from ground, compare Sect. 5.3 above. See also [WDD11, page 8A6-4].

All of this does not apply to launchers, which are short-lived, of course.

### 5.5 Availability of a Hardware-Based Memory Protection Unit

In the space domain, only the most recent space qualified microprocessors (e.g., LEON2/3) have some kind of memory management unit (MMU) available [WH09, Sect. VI.E]. The Leon2 processor provides two memory write protection registers only. This is not sufficient if security is relevant, too. The Leon3 processor has a full MMU and also provides read-protection [Mas+10a]. (Sect. 6.3.1 on page 21 below provides more details of the Leon processors.)

*Future work: describe current status concerning MPU in the aeronautical domain, in particular in IMA.*

### 5.6 Radiation

In the space environment, the high level of hard radiation causes frequent malfunctions or even the permanent destruction of electronic circuits. This radiation could be shielded by a substantially massive casing only. Its launch weight usually prohibits this solution. The effect of radiation can be reduced by using electronic circuits with larger chip structures, too. However, larger chip structures also mean less functionality per chip and less speed. Therefore, less powerful computers can be used in space than on ground.

The atmosphere of the Earth shields most of this radiation, even for aircraft at high altitudes. Therefore, the restriction does not apply to the aeronautical domain. Accordingly, aeronautical hardware such as IMA modules cannot simply be taken and used in the space domain.

Higher computing power may be obtained in the space domain by giving up reliability and availability for some tasks, to a certain degree. For example, a radiation-hard, but slow computer can take care of the vital tasks of the spacecraft, while a much faster "number cruncher" computer can perform payload data processing, for example video encoding, even though it will crash a few times a day. In order to not affect the vital system adversely, such a number cruncher needs a bus interface with validated high dependability, only. However, such an approach with differentiated hardware does not match well the idea of interchangeable IMA hardware components.

# 5.7 Miscellaneous: Differences Between Launchers and Satellites

Inside the space domain, there are notable differences between launchers and satellites. Launch vehicles live a short time only. The first stage is spent in a few minutes, and the launcher's payload ist deployed within hours, often even less. In contrast, satellites usually last at least months, and often more than a decade.

Accordingly, any comparison between the aeronautical domain and the space domain should state whether it refers to launchers or to satellites, if this matters.

# Chapter 6

# Existing Work on Time and Space Partitioning Suitable for Space Avionics

In this chapter, we survey existing work on time and space partitioning that is geared towards or particularly suitable for space avionics.

### 6.1 The IMA-SP Project: an Adaption of IMA for Space Avionics

### 6.1.1 The Original IMA-SP Project

Integrated Modular Avionics for Space (IMA-SP) [WDD11; WH09] was a project of the European Space Agency (ESA). It aimed at incorporating the benefits of time and space partitioning, based upon the aeronautical IMA concept, into the spacecraft avionics architecture. Windsor and Hjortnaes [WH09] motivate the benefits of IMA-SP in general, and they give an overview of the approach chosen, but yet without concrete experiences and without a defined, concrete architecture. Windsor *et. al.* [WDD11] provide such an architecture and some experimental applications of it.

The IMA-SP architecture is a two-layer architecture, consisting of a System Executive layer and an application layer [WH09]. The System Executive includes a software kernel responsible for partition scheduling and communication services as well as handling hardware signals. Memory partitioning is ensured either by a Memory Management Unit (MMU) or by a (simpler) Block Protection Unit (BPU). A BPU prohibits access to memory (at a minimum, write access) outside of a partition's defined memory areas. Partitions are scheduled on a fixed, cyclic basis. The order of partition activation is defined at configuration time using configuration tables. This provides a deterministic scheduling scheme. Tasks within a partition can be scheduled statically or dynamically. Temporal and spatial partitioning therefore ensures each partition uninterrupted access to common resources and non-interference during their assigned time period.

IMA-SP defines the role of the system integrator explicitly [WH09, Sect. III.D]. They are responsible for the system design including the detailed on-board resource allocation; and they are responsible for the final integration and configuration of the components. Furthermore, there are the role of the platform supplier and the role of the application supplier.

A communication bus is optional for the IMA-SP platform, for the case of a single hardware node

[WDD11]. This reflects the significantly smaller demands on communication in the space domain compared to the aeronautical domain, see Sect. 5.2.

The IMA-SP approach customizes its architecture quite specifically to the requirements of the space domain. Windsor *et. al.* [WDD11] list the following "user requirements":

- **Mode requirements:** Different partition scheduling plans shall be supported for different operational modes (e.g., initialization phase, operational phase, safe/survival phase).

- Allocation of basic physical resources: The resource allocation scheme shall be defined and predictable.

- Time services: The IMA-SP platform shall provide On Board Time (OBT) services.

- **On Board Events:** Applications may raise and access on-board operational events, such as launcher separation and alarms (for FDIR: Failure Detection, Isolation, and Recovery).

- Access to on-board data stores: There shall be on-board data stores for data generated between communication windows with ground, for mission programming data (e.g., longterm mission time line and telecommand files), for context data required to resume operations after a recovery action, and for software images and patches.

- Flight software maintenance: The applications and the kernel shall be maintainable via standard operations (dump, patch, and update).

- Fault protection: The IMA-SP platform shall support an FDIR service both at partition level and at system level.

- **Application communication interface:** Applications may interact with the platform or other applications through and only through well defined interfaces.

- **Observability requirements:** Ground shall have the possibility to reconstruct from telemetry the conditions leading to a change in a partition's state or an operational event being raised.

We think that these "user requirements" must make the resulting architecture rather specific for a narrow application area. The IMA-SP project apparently did not do a generalization step by identifying common requirements of the aeronautical domain and the space domain first, before adding the space specific requirements. Instead, the project put an emphasis on preserving longproven ideas, approaches, and even hardware from the space domain. Therefore, it has become less visible which conceptual changes are necessary for the transfer of IMA from the aeronautical domain to the space domain, and what are just customizations to a the specific application area. The aeronautical domain dared a more radical change of its ways when introducing IMA, compared to what the IMA-SP project is prepared to do.

We even think that the approach is tailored more to satellites than to launchers. Launchers have no opportunity to do flight software maintenance, and often there is no time for recovery from a safe mode.

Windsor et. al. [WDD11] describe the architecture of the IMA-SP platform. It is composed of:

- hardware node(s)

- a System Executive Platform (SEP), consisting of

- a partitioning kernel,

- a TSP abstraction layer, and

- (optionally) guest OSs inside the partitions

- system support services (e.g., for I/O) inside dedicated partitions

- application support services (e.g. implementations of standard protocols)

The services of the TSP abstraction layer were derived from the ARINC 653 [Aer05] API of the IMA architecture [WDD11]. In this, re-use of existing space concepts, which are similar to ARINC 653, took precedence over the (literal) incorporation of the ARINC 653 specification. Windsor *et. al.* describe the similarities and differences in detail [WDD11].

One example for a difference is that IMA-SP adds to IMA a set of services which allow to exchange data between partitions via shared memory. This is a mandatory addition. We think that this was driven by rather specific applications in mind. There appears to be no generalizing stock-taking of communication mechanisms which are or are not necessary for different application areas.

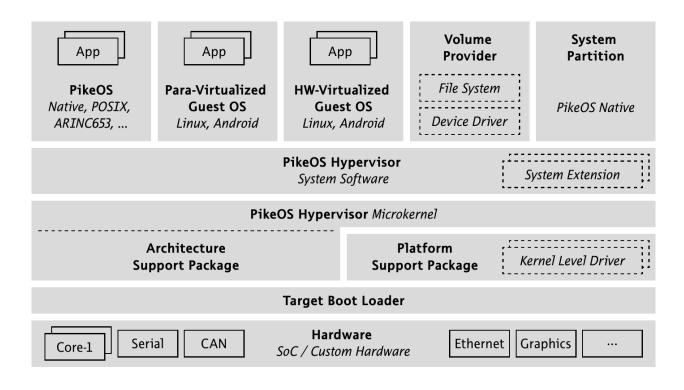

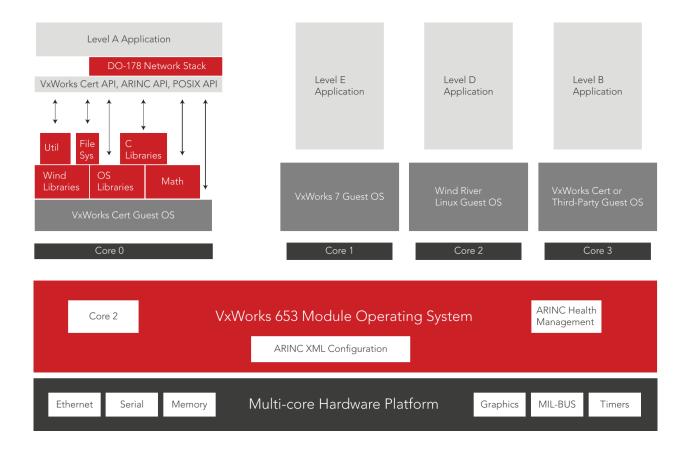

Three SEPs took part in the IMA-SP study: AIR (an RTEMS modification to support time and space partitioning by GMV, Portugal, see Sect. 6.3.4 below), PikeOS (a commercial microkernel from SYSGO, Germany, used in the the aeronautical domain, see Sect. 6.4.1 below), and XtratuM (an open source hypervisor from the University of Valencia, Spain, see Sect. 6.3.1 below). These SEPs have been ported to the LEON3 Sparc microprocessor which is the ASIC targeted for future European spacecraft [WDD11]. See the following sections for more details on these three SEPs.

Windsor *et. al.* [WDD11] report on three use cases which the IMA-SP study planned to investigate. In these use cases, it was planned to apply and try out the IMA-SP approach practically. Windsor presents some results in a talk at ADCSS 2012 [Win12]. The feedback on the system executive platforms was:

### "XtratuM:

Pro: product maintenance & adaptability - good level of maturity - OBT synchronisation

Cons: Missing GDB debug tool - bootloader

### Pike OS:

- Pro: Extensive documentation Development tools very good Easily configurable Debug available on TSIM

- **Cons:** No tracing mechanism Missing GDB debug tool RTEMS interrupt management not implemented

### Edisoft RTEMS:

[it was] para-virtualised for all SEP kernels"

And the conclusion of the talk included:

- "AIR, PikeOS and XtratuM have been ported to LEON2/3 and pre-validated – PikeOS offers DO-178 certification datapack

- Lessons learnt from Use Cases

- Mastering role definition and process is key to success

- IO management with current HW is challenging but not impossible

- Execution Platform support tools & test bench needed

- HW improvements have been identified"

Silva *et. al.* [SCS12] report on the development of an input/output component for IMA-SP, by GMV, Portugal. The aim is to be able to reuse the drivers for at least some system resources. It supports RS-232, UDP on Ethernet, SpaceWire and MIL-STD-1553B, in beta version quality.

The original IMA-SP project ended in December 2012.

### 6.1.2 Follow-Up Assessment Study on Partitioning and Maintenance of Flight Software in IMA-SP

Hardy *et. al.* [HHC14] report on a follow-up assessment study on partitioning and maintenance of flight software in IMA-SP. They ported a small satellite flight software to the Xtratum hypervisor on a (simulated) Leon3 processor. As some of the lessons learned, they provide experiences with the hypervisor used (XtratuM, compare Sect. 6.3.1 below) and with the guest operating system used (RTEMS, compare Sect. 6.3.4 below).

Concerning XtratuM, a few additions were made to XtratuM in order to support the boot scheme, the software maintenance approach, and the board chosen by the project. The authors report a bug found in the version 3.4.2 of XtratuM used as a major issue: A division-by-zero exception in the floating point unit of the processor halted the entire system. Thus, it could break the partitioning. Minor issues include that the virtualization of the registers of the LEON processor does not seem to be implemented correctly and completely. We conclude that the XtratuM version used did not yet meet quality criteria for a high level of dependability.

Concerning RTEMS, the authors found two bugs which they classified as major issues. One of them led to unpredictable scheduling inside the RTEMS partition. Both have been fixed in the latest version of RTEMS. However, the port of this version to XtratuM was still missing, at least at the time the presentation was made.

### 6.1.3 The IMA-SP System Design Toolkit Project

The IMA-SP System Design Toolkit project is a follow-up project to the original IMA-SP project. Hann *et. al.* [Han+15] describe its first phases (2014 to 2015). The project defined a data model, with associated files and file formats, describing the complete setup of a partitioned system and allowing for a system feasibility assessment; it developed a prototype of a tool set, called the IMA-SP System Design Toolkit (SDT); and it plans to demonstrate the toolkit on a case study.

The system feasibility assessment means to show that the partitioning and resource allocation meet all constraints and requirements. These include timing, fault containment, communication, and memory allocation. The system feasibility assessment is performed by the system integrator [Han+15].

The data model consists of, according to [Han+15]:

the partition model: partition properties, activities/tasks, communication ports, memory requirements, and resource requirements

the physical data model: memory, cache, interrupts, and peripheral devices

the IMA-SP system data model: allocation of physical resources to the partitions

the partitioning kernel data model: partitioning kernel memory requirements, health monitoring events and actions, default health monitoring system configuration table, and default health monitoring partition configuration table the partitioning kernel data model – configuration: health monitoring table, scheduling plan, connection table, and memory configuration table

the common data model: basic types of the data model

The IMA-SP SDT data model is specified using the "ecore" format, of the Eclipse Modelling Framework (EMF) project [Ste+08]. The model files are in XML Meta-data Interchange (XMI) format [ISO14].

Hann *et. al.* [Han+15] also further describe the system design work flow and the design of the IMA-SP System Design Toolkit.

### 6.2 The SAVOIR-IMA Initiative: A TSP Based Software Reference Architecture

SAVOIR (space avionics open interface architecture) is an initiative by the European Space Agency (ESA) which aims at improving the ways in which the European space community builds avionics sub-systems. It it geared towards satellites, thus excluding launchers. The initiative defined a reference avionics architecture for spacecraft platform hardware and software in general. The reference architecture either uses a "classic" execution platform or an execution platform providing time and space partitioning. SAVOIR is organized in specialized working groups. Two of them are SAVOIR-FAIRE on the software reference architecture in general and SAVOIR-IMA on the TSP based software reference architecture. [Hjo14]

Hiller and Hernek [HH13] report on the results and roadmap of the SAVOIR-IMA initiative. There are working groups and activities on:

- use cases and system requirements

- terminology

- reference architecture and interface description (COrDeT-3, SIFSUP)

- methods and tools for on-board software engineering

- adding multi core support to AIR (MultIMA)

- SW elements for security

- on-board software reference architecture for payloads (OSRA-P)

- IMA system design toolkit

- preparation for SEP kernel qualification package

The SIFSUP activity (Objectives of Savoir-IMA and Savoir-Faire Support) is, amongst others, on the difference in paradigm between IMA-SP (Time and space partitioning) and the On-board Software Reference Architecture (OSRA) (a component-based architecture on top of a centralized Execution Platform). [Jun14a]

On OSRA, see, e.g., Jung [Jun14b]. It does not cover time and space partitioning specifically. *Future work: find out more on SAVOIR-IMA.*

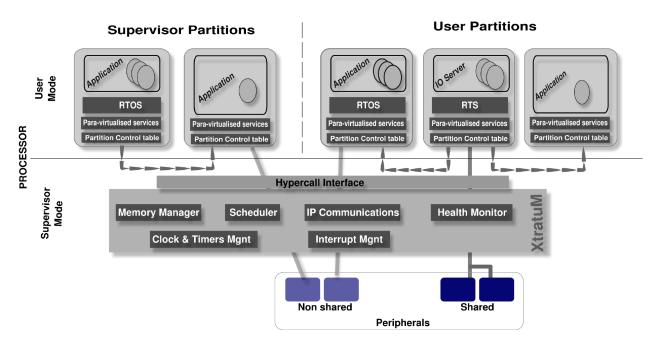

Figure 6.1: The XtratuM architecture, taken from [Pei+10, Fig. 1].

### 6.3 Virtualization Solutions Suitable for Space Avionics

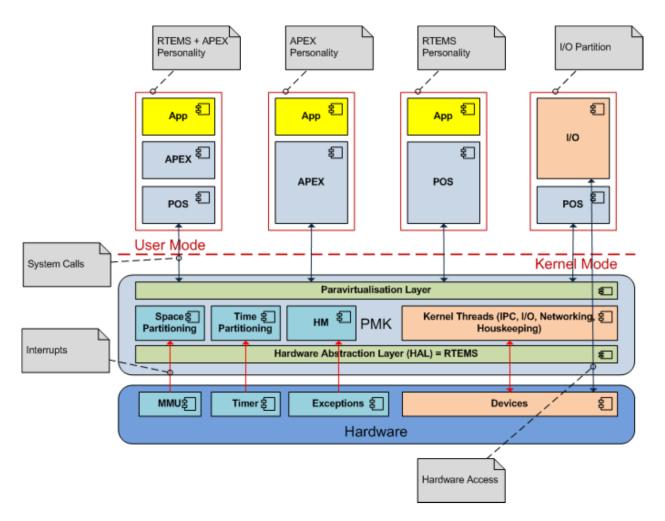

In this section, we survey virtualization solutions suitable for space avionics. They are the bare-metal hypervisor XtratuM and the partition management kernel AIR.

### 6.3.1 XtratuM: a Hypervisor for Safety-Critical Embedded Systems

XtratuM is a bare-metal hypervisor which implements para-virtualization and dedicated device techniques [Pei+10; Mas+09; Cre+09]. It was designed to achieve time and space partitioning for safety-critical embedded systems.

We already presented the notions of *virtualization in general*, of a *bare-metal hypervisor*, and of *para-virtualization* in Sect. 2.3.2 above.

Figure 6.1 shows an overview of the XtratuM architecture [Pei+10]. XtratuM executes in the supervisor mode of the processor. The applications execute in the user mode, each in its own partition. The hypervisor XtratuM applies a static scheduling scheme to grant execution time of the processor to the partitions. This achieves the separation of the partitions in the time domain. Each partition gets its statically determined share of the execution time. No user partition can overrun or change the schedule. Timer interrupts are caught and handled by the hypervisor.

Similarly, the hypervisor XtratuM allocates areas of memory to the partitions. It catches any illegal access to memory addresses outside a partition's memory space. To be precise, this is true only for processors providing suitable hardware support. The Leon2 processor does not have a memory management unit (MMU), which could translate virtual memory addresses into physical memory addresses. The Leon2 provides two memory write protection registers only. Therefore, XtratuM can enforce write protection among partitions, but not read protection. This is sufficient in order to meet safety requirements, but it is not sufficient to enforce security against malicious software in a partition. On processors providing a MMU, such as the Leon3 processor, XtratuM provides read protection, too [Mas+10a]. The Leon processors are designed for and used in a space environment, in particular with an increased level of radiation.

A peripheral device can be associated to a specific partition. In this case, no other partition may

access this peripheral device. This is similar to memory protection.

Some partitions may be special, these are called system partitions or supervisor partitions, in contrast to the user partitions. The system partitions are allowed to manage the other partitions, for example by stopping and resuming them via calls to the hypervisor. However, since these partitions run in the user mode of the processor, too, they cannot break the time and space isolation described above.

The XtratuM hypervisor provides a hardware abstraction to the partitions similar to the aeronautical ARINC 653 standard [Aer05] API of the IMA architecture (compare Sect. 4.3). However, these two interfaces have several differences. The most notable difference is that communication in the IMA architecture is based on the fast AFDX data network (compare Sect. 4.2), while XtratuM does not prescribe any particular network technology. There even can be no inter-computer network at all. This is probably due to the difference between the aircraft and the spacecraft domain, that communication demands are often lower in the latter domain, compare Sect. 5.2.

Each partition appears as a normal, dedicated computer to the software running in it. Accordingly, a partition can contain a bare application (no operating system at all, just an infinite loop), a general-purpose operating system, or a real-time operating system. In case there is some operating system, an application in a partition may have several processes/threads, as usual. The para-virtualization approach requires an adaption of the software inside the partitions, however: some privileged machine instructions in the lower layer of the operating system (or in the bare application) must be substituted by calls to the hypervisor, as discussed in Sect. 2.3.2.

Operating systems that have been ported to XtratuM include LithOS and RTEMS (see Sect. 6.3.4 on RTEMS below), and also Linux, PaRTiKle, and ORK+ [FEN+13]. The real-time operating system LithOS [Mas+10b] was designed to provide an ARINC 653 inspired API. LithOS adds multi-process support, communication between processes, and a process scheduler to the services provided by XtratuM. However, there is still no mandatory AFDX network with LithOS. Similarly, PaRTiKle is an open source real-time kernel for embedded systems, distributed under the terms of the GNU Public License; PaRTiKle has been initially developed by the University of Valencia, Spain [FEN+13]. ORK+ (Open Ravenscar Kernel) is a small, high performance real-time kernel that provides restricted tasking support for Ada programs [FEN+13].

The processors on which XtratuM has been implemented include the Intel x86 processor family, supporting multiprocessors [Mas+09; Cre+09], the Leon2 processor [Pei+10], the Leon3 processor [Mas+10a], the Leon4 processor [Cre+14; MCC12], and the ARM Cortex R4 [Cre+14]. XtratuM has been adapted to deal with heterogeneous multicore architectures in the MultiPARTES project, see Sect. 6.3.3 below.

XtratuM is open software distributed under the Gnu Public Licence version 3. Some ancillary tools are sold under a proprietary licence by FentISS [Fen16], a spin-off of the University of Valencia, Spain.

The configuration of a specific software image must be described in a central configuration file. XtratuM's system integration tools compile this configuration file together with the application software images into the system software image. This image then is loaded onto the processor an run.

The central XtratuM configuration file is in XML format and can be written by hand. Alternatively, the configuration file can also be generated using the Xoncrete tool. Xoncrete is a graphical tool to assist the system designer when configuring the resources (memory, communication ports, devices, processor time, etc.) allocated to each partition. It has two parts: a resource editor and a scheduling analysis tool [Bro+10]. The scheduling analysis tool provides support for the complexities of hierarchical scheduling (i.e., scheduling the partitions and scheduling tasks inside

Figure 6.2: The attitude control demonstrator.

the partitions) [Bro+10; Rip+10].

**Maturity:** The study of Hardy *et. al.* [HHC14] (see Sect. 6.1.2 above for details) indicates that the XtratuM version 3.4.2 used there did not yet meet quality criteria for a high level of dependability.

# 6.3.2 Our Case Study Using XtratuM for a Portable Real-Time Application

We performed a case study using XtratuM [Ehr+15]. It used an e.Cube computer designed by AirbusDS for space missions, featuring an x86-family Atom processor. The application was an attitude control demonstrator with one degree of freedom, see Fig. 6.2. The application ran on the Atom processor inside one of the XtratuM partitions. The application ran bare-metal, only using XAL (the XtratuM Abstraction Layer), without an operating system. (It had turned out that the port of the Linux operating system to XtratuM didn't run anymore in the then current version of XtratuM.) The application had real-time properties. It had to be formally proven that these real-time requirements were met by the implementation running on top of XtratuM.

The project was performed in a collaboration of the City University of Applied Sciences Bremen with AirbusDS, Bremen.

The goals of the project included gaining familiarity with real-time systems and in particular with real-time proofs. The proofs based on the idea of determining the worst-case execution time by testing with exhaustive path coverage. Furthermore, the effort necessary for achieving portability of the software (including the real-time proofs) to other hardware architectures was of interest.

The project provided experience with XtratuM. We used XtratuM version 3.7.3, current as of September 2014. It turned out that the adaption of XtratuM to the specific main board could be solved only partially due to missing documentation of the details of the main board used. Configuring the software image for the hardware and the applications needed substantial effort. It would probably have been of considerable help if the Xoncrete tool for XtratuM would have been

available for this.

Preparatory work for the real-time proofs was performed. But due to delays because of the hardware adaption problems mentioned, the full proof was not carried out anymore.

In retrospect, using a hypervisor like XtratuM has the advantage that several applications with different criticality can run safely on a single processor; but there were no indications that the hypervisor would ease porting the application and its real-time proof to another hardware architecture. The reason for this is that the hypervisor does not abstract away from the details of the hardware used, they remain fully visible to the application. The hypervisor only hides the other partitions running on the same processor. We did not attempt to port the application to another processor anymore in the course of the project. But both the compiled application binary and the real-time proof depend on the specifics of the processor. Of course, the application can be compiled for a different processor. But using a hypervisor makes no difference in this. The same holds for adapting the real-time proof to another processor and its timing characteristics.