# FPGA Based Active Camera Stabilization for a Small Satellite Designing a Digital Control

Benjamin Bissendorf

Jan Bredereke Simon Pfennig Janek Brumund Niklas Seeliger Joscha Knobloch

Hochschule Bremen Flughafenallee 10, 28199 Bremen

March 4, 2024

#### **Abstract**

#### written by Jan Bredereke

We investigate how an active control can stabilize a satellite's on-board camera in an inexpensive way, disturbed by micro-vibrations coming from the reaction wheels of the Attitude Determination and Control System (ADCS), and maybe also disturbed by its orbital movement. In particular, in this project we investigate how to design the digital part of the control. We use an active control running in the FPGA of a PYNQ-Z2 board. The control is a PID controller, adjusted experimentally. It turns out that obviously it will be feasible to implement the digital part in this way. We did not have the time and human resources for a complete implementation of the digital part. But all digital components have either been implemented or at least shown to be implementable. The mechanical part of a test bed was provided to us by the VIBES project; we didn't intend to work on it. Nevertheless, we conceived several improvements, and we implemented a few of them. Finally, we identify in detail the work that needs to be done, both on the digital part and on the mechanical part, such that we can conduct an experimental proof that the control indeed reduces micro-vibrations as intended.

## Acronyms

AXI Advanced eXtensible Interface

**DMA** Direct Memory Access

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

**GPIO** General Purpose Input / Output

**IP** Intellectual Property

I2S Inter Integrated Chip Sound

LSB Least Significant Bit

PCB Printed Circuit Board

PL Programmable Logic

**PS** Processing System

SPI Serial Peripheral Interface

# Contents

|   | Acro  | onyms                                                                      | iv |  |  |  |

|---|-------|----------------------------------------------------------------------------|----|--|--|--|

| 1 | Intro | ntroduction                                                                |    |  |  |  |

|   | 1.1   | Context of the Project                                                     | 1  |  |  |  |

|   | 1.2   | Research Question of the Project                                           | 1  |  |  |  |

|   | 1.3   | Related Work                                                               | 1  |  |  |  |

| 2 | Our   | Approach to Reducing Disturbances                                          | 2  |  |  |  |

|   | 2.1   | Reducing Micro-Vibrations by the Attitude Determination and Control System | 2  |  |  |  |

|   | 2.2   | Mitigating Orbital Movement                                                | 3  |  |  |  |

| 3 | Med   | chanical Concept of the First Version of The Test Bed                      | 4  |  |  |  |

|   | 3.1   | Design Rationale                                                           | 4  |  |  |  |

|   | 3.2   | Geometry of the Test Bed                                                   | 4  |  |  |  |

|   | 3.3   | Evaluation of the Geometry of the Test Bed                                 | 4  |  |  |  |

| 4 | Med   | echanical Concept of Our Second and Third Versions of The Test Bed         |    |  |  |  |

|   | 4.1   | Design Rationale                                                           | 6  |  |  |  |

|   | 4.2   | Improved Geometry of the Test Bed                                          | 7  |  |  |  |

|   | 4.3   | Partial Implementation in the Second Version                               | 9  |  |  |  |

|   | 4.4   | The Electrical Interfaces of the Test Bed                                  | 10 |  |  |  |

|   | 4.5   | Research Question for the Second and Third Version of the Test Bed         | 11 |  |  |  |

|   | 4.6   | Measuring Vibrations Around the Third, Line-of-Sight Axis                  | 12 |  |  |  |

| 5 | The   | eoretical Background                                                       | 13 |  |  |  |

|   | 5.1   | AXI                                                                        | 13 |  |  |  |

|   |       | 5.1.1 AXI-Lite                                                             | 13 |  |  |  |

|   |       | 5.1.2 AXI-Stream                                                           | 14 |  |  |  |

|   |       | 5.1.3 AXI-Interconnect                                                     | 14 |  |  |  |

|   | 5.2   | SPI                                                                        | 14 |  |  |  |

|   | 5.3   | The Processing System and Python                                           | 15 |  |  |  |

|   | 5.4   | Sensors                                                                    | 15 |  |  |  |

|   | 55    | Actors                                                                     | 15 |  |  |  |

| 6  | Con        | cept for the digital control system                  | 17           |

|----|------------|------------------------------------------------------|--------------|

|    | 6.1        | Configuration                                        | 17           |

|    | 6.2        | Input Interface                                      | 18           |

|    | 6.3        | Digital Controller                                   | 18           |

|    |            | 6.3.1 Filters                                        | 19           |

|    |            | 6.3.2 Deflection Estimator                           | 19           |

|    |            | 6.3.3 Controller                                     | 22           |

|    | 6.4        | Output Interface                                     | 23           |

|    |            | 6.4.1 Inter Integrated Chip Sound (I <sup>2</sup> S) | 23           |

|    |            | 6.4.2 Configurator                                   | 24           |

|    |            | 6.4.3 Soundmultiplexer                               | 24           |

|    | 6.5        | Validation Data                                      | 25           |

| 7  | Imnl       | lementation of Input Interface                       | 26           |

| •  | 7.1        | ·                                                    | 26           |

|    | 7.1        | 7.1.1 AXI Lite interface                             |              |

|    |            |                                                      | 27           |

|    |            | •                                                    | 28           |

|    | 7.2        |                                                      | 28           |

|    | 7.3        | ·                                                    | 30           |

|    | 7.4        |                                                      | 30           |

| 8  | lmnl       | lementation of Digital Controller                    | 31           |

| U  | 8.1        |                                                      | 31           |

|    | 0.1        |                                                      | 31           |

|    |            | 8.1.2 High Pass Filter                               | 32           |

|    | 8.2        | Deflection Estimator                                 |              |

|    | 8.3        | Controller                                           |              |

| ^  |            |                                                      | 25           |

| 9  | 9.1        | ·                                                    | <b>35</b> 35 |

|    |            |                                                      | 36           |

|    | 9.2<br>9.3 | g .                                                  | 36           |

|    | 9.5        | Soundinardprexer                                     | 30           |

| 10 | Impl       | lementation of Configuration                         | 40           |

|    | 10.1       | Configuration from the PL-Side                       | 40           |

|    | 10.2       | Configuration from the PS-Side                       | 41           |

| 11 | Impl       | lementation of Validation Data                       | 42           |

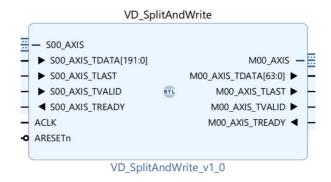

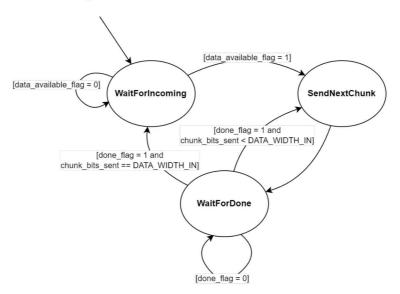

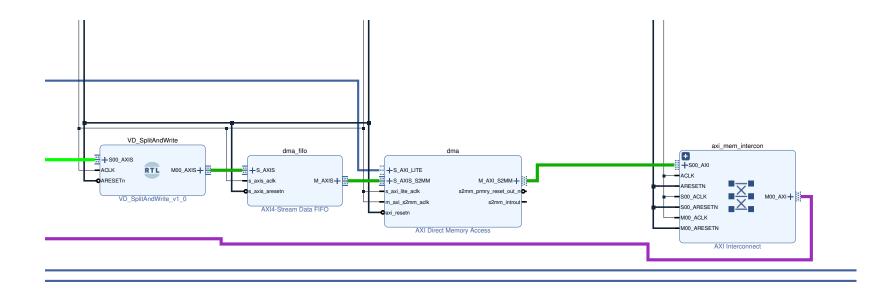

|    | 11.1       | Split and Write                                      | 42           |

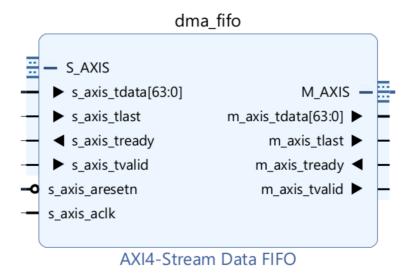

|    | 11.2       | FIFO Buffer                                          | 44           |

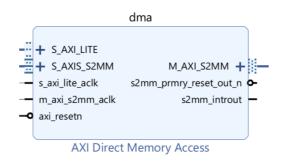

|    | 11 3       | AXI DMA Controller                                   | 44           |

|    | 11.4 Collect and Log                           | 46  |

|----|------------------------------------------------|-----|

|    | 11.5 Test                                      | 49  |

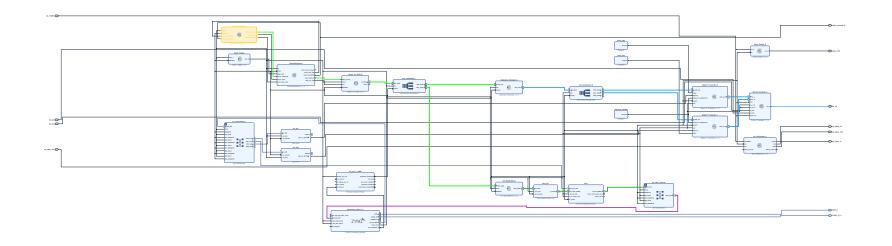

| 12 | ? Integration                                  | 50  |

|    | 12.1 System level integration                  | 50  |

|    | 12.2 Start of operation                        | 51  |

| 13 | 3 Evaluation                                   | 52  |

| 14 | Summary                                        | 53  |

|    | 14.1 Digital Part of the Control               | 53  |

|    | 14.2 Mechanical Part                           | 53  |

| 15 | Future Work                                    | 55  |

|    | 15.1 Digital Part of the Control               | 55  |

|    | 15.2 Mechanical Part                           | 57  |

|    | 15.3 Experimental Proof of Vibration Reduction | 58  |

| Α  | Code                                           | 61  |

|    | A.1 SplitAndWrite                              | 61  |

|    | A.2 SensorSequencer                            | 64  |

|    | A.3 Sensor Dummy                               | 66  |

|    | A.4 Deflection Estimator                       | 68  |

|    | A.5 Digital P Controller                       | 74  |

|    | A.6 Sensor Communication top level             | 78  |

|    | A.7 Sensor Communication                       | 81  |

| В  | Filter Coefficients                            | 98  |

| С  | ADAU1761 configuration                         | 99  |

| D  | Block Designs                                  | 101 |

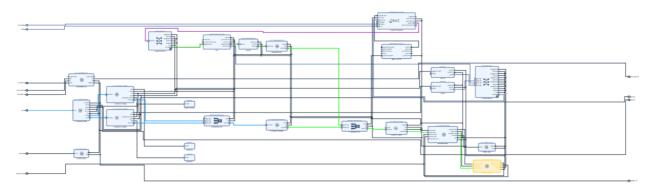

|    | D.1 Digital Controller Design                  | 101 |

|    | D.2 Validation Data Design                     | 102 |

|    | D.3 System Design                              | 103 |

## Introduction

written by Jan Bredereke

#### 1.1 Context of the Project

The project "FPGA Based Active Camera Stabilization for a Small Satellite" is part of the elective module "Embedded Systems" of Jan Bredereke. The project is conducted in the context of the research project VIBES of the City University of Applied Sciences Bremen. VIBES investigates micro-vibrations in satellites. Such micro-vibrations degrade the quality of photos of an on-board camera used for scientific Earth observation. The micro-vibrations come from the reaction wheels that are part of the Attitude Determination and Control System (ADCS), in particular.

The project VIBES is headed by Antonio García. VIBES plans to investigate the micro-vibrations using CubeSat small satellites. It also aims to try out solutions practically in this way. VIBES will launch an entire series of CubeSats. The first CubeSat is scheduled to launch in the end of the year 2024.

### 1.2 Research Question of the Project

The development of the CubeSats encompasses a wide palette of aspects and tasks. The project of the elective module "Embedded Systems" of Jan Bredereke concentrates on one of these aspects, which is the research question:

How can an active control stabilize a satellite's on-board camera in an inexpensive way, disturbed by micro-vibrations coming from the reaction wheels of the ADCS, and maybe also disturbed by its orbital movement?

#### 1.3 Related Work

Little detailed information is publicly available on micro-vibrations. Companies building satellites probably have no interest in sharing their results with their competition. A notable exception are handbooks by the European space agency ESA ([ECSS13; ESSB11]) and at least one conference paper ([SVP19]).

An internship report ([Ger23]), written in the context of VIBES, selects an optical system which can be used to visualize the degrading effect of micro-vibration on images. It analyzes the effects of micro-vibrations and of orbital motion. It does not investigate counter-measures.

# Our Approach to Reducing Disturbances

written by Jan Bredereke

# 2.1 Reducing Micro-Vibrations by the Attitude Determination and Control System

Several ways of reducing disturbances by micro-vibrations are conceivable:

Passive isolation is probably not sufficient.

Active control with an actor must be fast. It can be done either with a microcontroller or with an FPGA.

Active compensation using a counter-vibration, with a (slowly) controlled amplitude and phase, is less efficient, rather more difficult to realize, and therefore not necessary.

All electronics needs to withstand space radiation, requiring large structural widths on the chips, and consequently are slow.

The following arguments influence our choice between a microcontroller and an FPGA solution:

A microcontroller requires a real-time operating system, because of the high control frequency. Other on-board software needs a conventional operating system. This might necessitate a dedicated microcontroller. Using a microcontroller for micro-vibration control thus is feasible, but needs valuable space, weight and electricity.

The software defined radio of the CubeSat already uses a PYNQ-Z2 board comprising a microcontroller and an FPGA. This microcontroller runs a conventional operating system. Only a small part of the FPGA in the PYNQ-Z2 is used, up to now.

Therefore we decided for an active control running in the FPGA of the PYNQ-Z2.

Two approaches are available for designing the control:

An analytical modelling of the controlled system requires a lot of control theory. And it requires a lot of details on the experimental setup.

A PID controller, adjusted experimentally, needs less knowledge of control theory. It is independent of the experimental setup.

Therefore we chose a PID controller, adjusted experimentally.

### 2.2 Mitigating Orbital Movement

The disturbances due to the orbital movement can be mitigated by making the camera follow its field of view on Earth. This can be done either by swivelling the entire satellite, or by moving the camera only. The former puts demands on the Attitude Determination and Control System. The latter might be realized by an extension to the micro-vibration control already discussed.

We do not investigate further this aspect for the time being. But we keep in mind that it may prove advantageous to have actors for micro-vibration control which also allow for movements suitable for orbital movement mitigation.

# Mechanical Concept of the First Version of The Test Bed

written by Jan Bredereke

The project VIBES provided a first version of a test bed to us.

#### 3.1 Design Rationale

The approach of the project VIBES is to keep the test bed as simple as possible; the test bed thus assumes that vibrations are strictly translational and not rotational. This simplification comes from previous experiments. These experiments proved that it is possible to measure micro-vibrations at all. Since translational movements are simpler than rotational ones, the simplification was kept for the first version of the test bed here.

#### 3.2 Geometry of the Test Bed

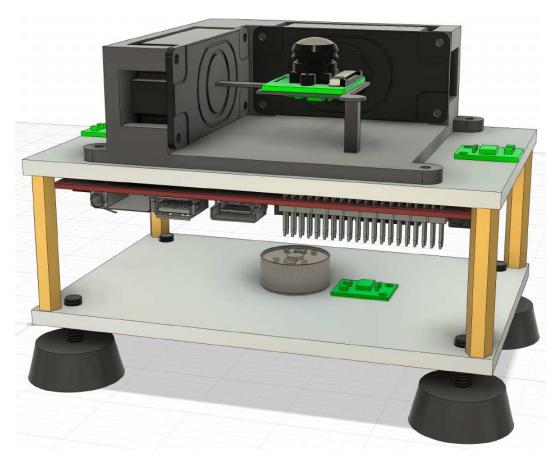

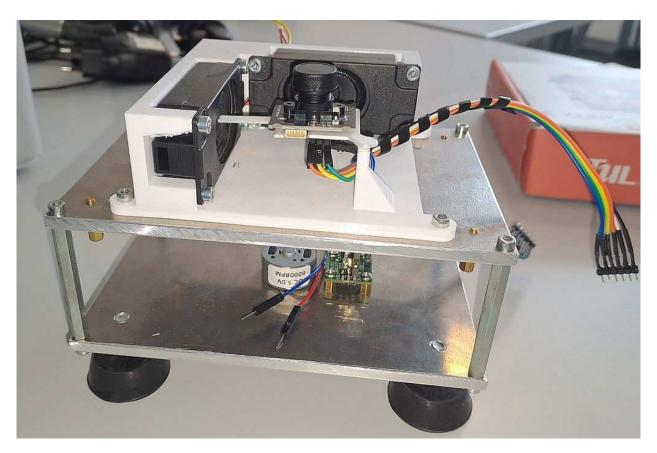

The first version of the test bed consists of two heavy and rigid metal plates, connected by four supporting stands (compare Fig. 3.1 and Fig. 3.2 on the facing page). The lower plate carries a motor capable to run at up to 6000 rpm. It carries an acceleration sensor close to the motor, too. The upper plate carries two audio speakers. The movable parts of these speakers are connected by a thin and light, L-shaped, 3D-printed carrier plate. The carrier plate in turn carries a camera and another acceleration sensor. Both acceleration sensors each are part of a small printed circuit board which allows to solder wires to it. A USB cable from the camera and another cable from the acceleration sensor near the camera lead away from the camera plate. Rubber feet support the entire setup. The off-the-shelf rubber feet are rather stiff.

## 3.3 Evaluation of the Geometry of the Test Bed

The first version of the test bed would not allow us to design a micro-vibration control system, neither for translational vibrations nor for rotational vibrations. This version is designed for the simplification to translational vibrations. But, inevitably, it will have rotational vibrations, too, interacting with the translational sensors.

Furthermore, the cabling needs improvement. The cables from the camera platform are thick and stiff. They are bound to introduce non-linearities, which additionally will change after every touching of the setup. (We keep the choice of using USB, though. Its four wires are way better than what most of the affordable RasPi cameras offer: a 15-wire flat ribbon cable.)

Consequently, we improved the concept of the test bed.

Figure 3.1: Construction drawing of the first version of the test bed. (source: [Wit23])

Figure 3.2: Photo of the first version of the test bed. (photo: Winfried Sembritzki)

# Mechanical Concept of Our Second and Third Versions of The Test Bed

written by Jan Bredereke

This section describes our changes to the test bed and the reduced research question for this iteration. Furthermore, we explain that an additional, interesting measurement becomes possible.

Due to strict time constraints, we could not implement all of our ideas from the start of the term. Therefore we describe the second version of the test bed, which we actually realized, and we describe a third version which we propose to make the test bed fit for use in testing.

#### 4.1 Design Rationale

Our second and third version of the test bed discard the problematic simplification to translational vibrations. We now aim for reducing the rotational vibrations using our control system. This has the advantage of coming closer to the real task; only rotational vibrations are relevant in orbit.

En-route we also improve the mechanics of the cabling.

We do not expect the third version of the test bed to be the final, definitive one. Quite likely, there will be some resonances and other mechanical deficiencies.

Our goal is to demonstrate the feasibility of designing an electronic control system able to reduce micro-vibrations at frequencies of up to 1 kHz. The demonstration shall be done at at least one frequency. Our emphasis is on the electronic part. Improving the mechanical part is left to future iterations of the setup.

Similarly, we will not evaluate the images of the camera for blurring. Consequently, the second, implemented version does not comprise a camera. And the envisioned third version could use a dummy camera of similar weight and size, unless there is sufficient time for evaluating the images of a camera, too. Such an evaluation should use a camera with a narrow angle of view, requiring the cost of purchase.

Our second and third versions require three acceleration sensors. In order to reduce the cost for them, we are prepared to increase the amplitude of the micro-vibrations, if necessary. The electronics of our vibration control system is independent of the actual amplitude of the vibrations, except for sensor noise. Sensors with less noise are more expensive. Therefore, we rather increase the amplitude of the vibrations than invest in sensors of a higher quality. The project VIBES already did prove that micro-vibrations can be measured with affordable sensors. We do not need to repeat this work here. Of course, a final version of the test bed must have both the electronics system and sensors of sufficient sensitivity.

#### 4.2 Improved Geometry of the Test Bed

The third version of the test bed we envision keeps the main body with the motor for generating vibrations and with the PYNQ-Z2 board. We replace the upper part with the camera platform and with the actors only.

The camera is mounted on a movable plate held by a flexible rod. It thus can rotate around two axes, when the rod is bent. (In principle, it can also twist around the third axis, the line-of-sight of the camera. We will come back to this in Sect. 4.6 on page 12.) The line-of-sight of the camera is still going straight upward from the plate.

The plate now isn't pushed from two sides anymore. Instead, it is pushed from below by two actors. These actors are placed 90° apart when viewed along the axis of the rod. This allows the two actors to rotate the plate around two axes independently.

The actors are small speakers. They can handle the maximum frequency necessary easily. They are cheap. And they can be purchased off-the-shelf. Figure 4.1 shows the 3D-printed mount for the speakers. (Unfortunately, the speakers purchased do not fit this mount. Their dimensions advertised differ from their actual dimensions.)

Figure 4.1: 3D-printed mount for the speakers. (photo: Winfried Sembritzki)

The size of the plate is wide enough to reach over the speakers.<sup>1</sup> When they push upward, they push the middle of an edge of the plate. Having small speakers, and placing them close to each other, yields the advantage that the plate can be made smaller and thus lighter.

The speakers must be able to bear 3 W of power from the existing audio amplifier. This prevents inadvertent destruction by experimentation errors.

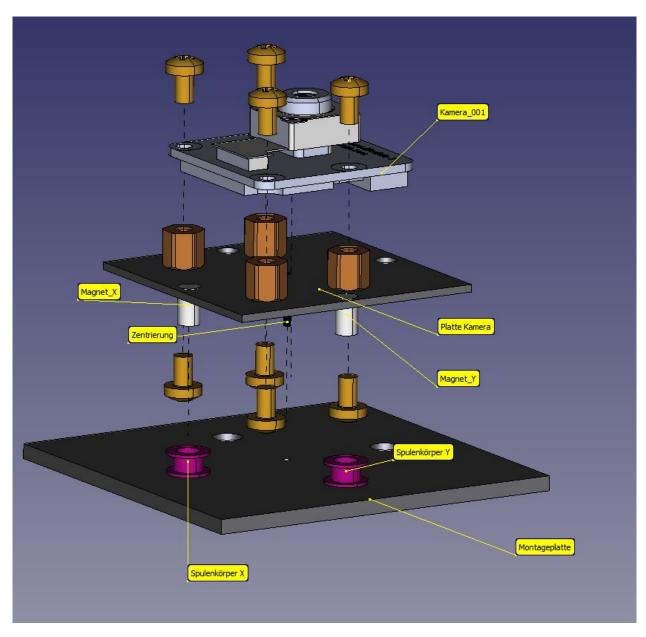

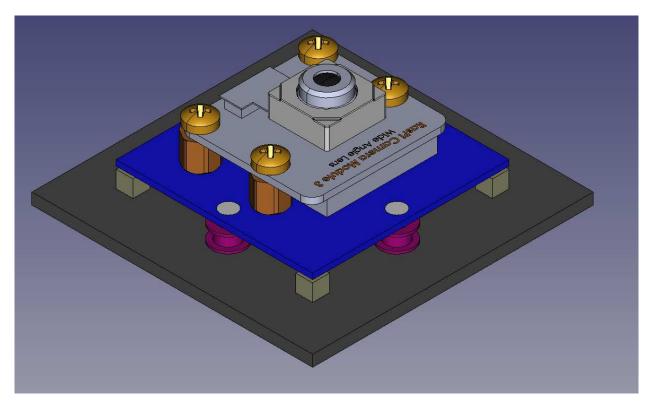

Beyond our third version, we envision improved designs of the actors. A custom actor can be made of a magnet and a coil. This would be much smaller and more robust. Figure 4.2 on the next page and Fig. 4.3 on page 9 show drawings of a camera mount with such actors. The coils are drawn in violet color. However, we did not have the time to iterate through several versions of such a custom actor, which are likely to be necessary. A piezo actor might be possible, too, depending on the maximum amplitude necessary. Since a single piezo actor typically achives a few micrometers only, we did not risk to follow this approach for now. If possible, a piezo actor should be preferable, due to its even more increased

<sup>&</sup>lt;sup>1</sup>Actually, the speakers purchased are too large for the plate used. But since they do not fit their mount anyway (see above), a mechanical redesign is necessary here in any case.

Figure 4.2: actors made of a magnet and a coil: explosion drawing. (drawing: Winfried Sembritzki)

robustness and even smaller size.

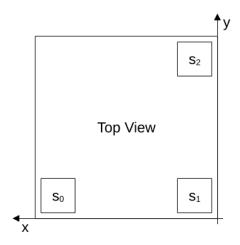

The plate with the camera carries a printed circuit board (PCB) with the acceleration sensors. They are arranged in an L shape. They are placed in three of the four courners of the quadratic plate/PCB. For measuring the rotational accelerations, we use the sensors' direction vertical to the plate only. The difference of the accelerations of two adjacent sensors describes the rotational acceleration around the axis perpendicular to their connecting line. One sensor is part of two such differential arrangements.<sup>2</sup> The axes of both arrangements are lined up with the axes of the acctors.

We use thin, light, flexible and short individual wires for connecting the movable camera plate with the main body of the test bed. These wires replace the thick and stiff cables of the previous version. Both the sensors' SPI bus and the camera's USB are connected in this way. The short length allows to have no shielding for the USB wires. We use a stripboard mounted close to the camera plate for having a mechanically robust starting point for the conventional further cabling.

We use softer, 3D-printed feet, instead of the off-the-shelf feet of the first version of the test bed.

<sup>&</sup>lt;sup>2</sup>Sensor noise can be reduced by using all three sensors for each axis: instead of computing the difference between a sensor A and a sensor B, we can compute the difference between the sensor A and the mean of sensor B and sensor C. This improvement depends on a sufficient mechanical precision of the setup, such that both axes remain decoupled.

Figure 4.3: actors made of a magnet and a coil: assembled drawing. (drawing: Winfried Sembritzki)

We use none of the acceleration sensors of the first version anymore. The sensor on the camera platform has been removed. And the second sensor close to the motor is still there, but does not provide us with information of interest.

### 4.3 Partial Implementation in the Second Version

As stated, we could not implement all of the above ideas for the third version. We had to leave out the following aspects:

- The speakers are not yet in place. This is due to the fact that they do not fit into the 3D printed mount.

- Instead, we use the speakers of the first version, mounted into the testbed of the first version. This allows us to validate that the speakers generate movements (which should be audible). But there is no mechanical connection from the speakers of the first version to the sensors of the second version.

- The printed circuit board for the movable plate is not yet mounted on a flexible rod. Instead, it is mounted temporarily onto a stripboard. However, thin wires are used already.

- The softer, 3D-printed feet are still missing.

- The camera (dummy) is still missing.

In consequence, the mechanical realization allows to implement the electrical part from sensors to actors, but the mechanical loop from the actors back to the sensors is in concept stage only.

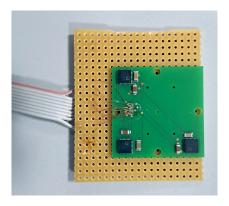

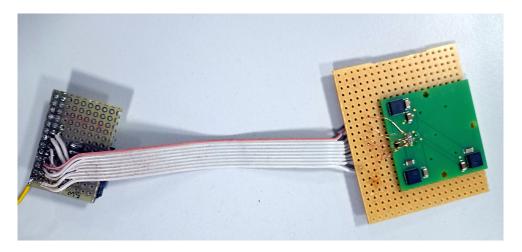

Figure 4.4 on the next page shows the printed circuit board for the movable plate. In the photo, the green printed circuit board (PCB) is mounted onto a yellowish stripboard temporarily. Please note the thin wires leading off the printed circuit board. Figure 4.5 on the following page shows the same PCB, and also the adapter at the other end of the cable from the stripboard.

Figure 4.4: printed circuit board for the movable plate of the second version of the test bed. (photo: Winfried Sembritzki)

Figure 4.5: printed circuit with the sensors and also the adapter at the other end of the cable from the stripboard. (photo: Winfried Sembritzki)

#### 4.4 The Electrical Interfaces of the Test Bed

The electrical interfaces of the third version of the test bed comprise:

- SPI bus for 3 sensors with 3 sub-sensors each, from stripboard to PYNQ board:

1 bus (4 wires) plus 3 chip select wires

- USB of camera, from stripboard to PYNQ board

- 2 audio connections, from amplifier to PYNQ board:

3 wires total, headphone jack

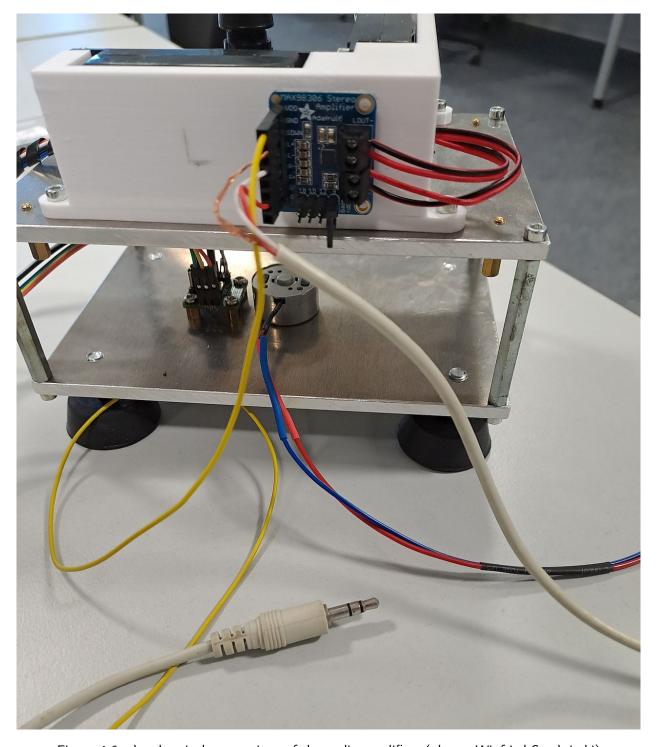

(see Fig. 4.6 on the next page)

- motor power, from motor to (still missing) power driver:

2 wires

- PWM motor signal, from (still missing) power driver to PYNQ board:

2 wires

- USB for power and FPGA loading, from PYNQ board to external

ethernet, from PYNQ board to external:

(as soon as the microcontroller leads out measurement data and leads in PID parameters and motor speed parameter)

Figure 4.6: the electrical connections of the audio amplifier. (photo: Winfried Sembritzki)

# 4.5 Research Question for the Second and Third Version of the Test Bed

For our iteration with the second and third versions of the test bed, we reduce our research question in Sect. 1.2 on page 1 to:

How can an active control stabilize a camera-like dummy using an FPGA-based digital circuit, disturbed by vibrations at one frequency close to 1 kHz?

#### 4.6 Measuring Vibrations Around the Third, Line-of-Sight Axis

Our arrangement of the sensors pays us a bonus: we can measure the rotational vibration around the third axis, which is the line-of-sight of the camera. We have no actor to counter this rotational vibration. But we can measure its angular amplitude, and we can calculate whether this angular amplitude causes the pixels in the camera to shift less than one pixel wide.

For measuring, we use the sensor's sub-sensors which are in the plane of the camera plate. (Each sensor consists of three sub-sensors in three differen directions.) Again, the difference of the accelerations of two adjacent sensors yields a value for the rotational acceleration. The difference of the accelerations of the two non-adjacent sensors, for two perpendicular directions, yields another value for the rotational acceleration. In total, we get three values from six applicable sub-sensors. By taking the mean value from these three values, we can reduce the noise of the sensors. It is advisable to calculate the total rotational acceleration directly from the values of all six sub-sensors in order to give each of them the same weight.

## Theoretical Background

#### 5.1 AXI

written by Simon Pfennig

The Advanced eXtensible Interface (AXI) is a Protocol for communication between a Master and a Slave component. The communication is always initialized and controlled by the Master. There are two types of Transactions, Read and Write, which allow the Master to either read or write the contents of registers in the Slave Component. See [AMD23] for the specification. Data is transmitted in words, where each bit of a data word has its own line.

#### **5.1.1 AXI-Lite**

AXI-Lite is a bare-bones version of AXI. The mechanisms described below are true for AXI-Lite as well as the regular AXI. Features not used by AXI-Lite, like Transaction-IDs and Regions, are not used in this project and are therefore not described.

Read transactions are facilitated by two channels: Read-Address and Read-Data. The transaction is initialized by the Master sending the address of the register it wants to read on the Read-Address channel followed by the Slave responding with the corresponding data on the Read-Data channel.

Write transactions are facilitated by three channels: Write-Address, Write-Data, and Write-Response. The Master will first write the address he wants to set on the Write-Address channel, followed by the data on the Write-Data channel. Afterwards, the Slave will respond, on the Write-Response channel, with a status code indicating whether the transaction was successful.

Before something is written on any channel a handshake (see Figure 5.1 below) is performed to ensure both sender and receiver can process the data. Therefore every channel has, aside from the actual data signals, a Ready and Valid signal. The Valid signal is set by the sender when the data on the data signals is set to the actual data that is to be transmitted. The Ready signal in turn is set by the receiver to indicate it is ready to process the data. On the first rising edge of the clock when both are set the data is transmitted and both Valid and Ready are set to 0.

Figure 5.1: AXI Handshake [AMD23]

#### 5.1.2 AXI-Stream

AXI-Stream (see [AMD21] for the specification) is a version of the AXI-Protocol that only uses one data channel. The only mandatory components are the clock and reset signals, as well as the data signals, the TValid, and TReady signal. Since there are no addresses involved and the Slave can not send but only receive data, AXI-Stream can be used for high-throughput one-directional use cases. This project also uses the TLast signal which is used to indicate that the transmitted data packet was the last one in a sequence.

#### 5.1.3 AXI-Interconnect

The AXI-Standard only describes the communication between a single Master and a single Slave. But in practice, a single Master often needs to control multiple Slaves, or multiple Masters control the same Slave. An Interconnect is a component that enables these types of communications. It has multiple AXI-Slave and AXI-Master ports for various other components to connect to. When a master addresses a Slave, the address data is used by the interconnect to decide to which Slave it should forward the message to and vice versa. It also arbitrates when multiple communications are requested at the same time. In this project the "AXI Interconnect v2.1 LogiCORE IP" is used. See [AMD22a] for the documentation. This IP-Core also implements a translation between different AXI-Versions spoken by Master and Slave. This allows AXI-Lite components to communicate with regular AXI components.

#### 5.2 SPI

written by Joscha Knobloch

Serial Peripheral Interface (SPI) is a synchronous bus meant for connecting multiple peripheral devices with a single host device. It uses a single data line per direction, a separate clock line, and chip select lines per sub.

Different naming schemes are common and a renaming is ongoing in the industry. The common naming before the current renaming is Master for the host device, Slave for the peripheral device, MISO(Master in Slave out), MOSI(Master out Slave in), SS(Slave select), and CLK(Clock). Current renaming efforts commonly use Main(formerly Master), Sub(formerly Slave), SDO(Serial Data Out, formerly MOSI), and SDI(Serial Data In, formerly MISO). The naming for the clock line is usually kept.

The main device controls the clock line, which is used to indicate a transmission. When the main device does not intend to transmit data, the clock is kept idle. This design means that the transmission is always bidirectional and the protocol over top is in charge of discarding unneeded transmissions in one direction.

To access any of the connected subs the main has individual chip select lines going to each sub. This allows for a trivial sub-selection but increases the need for output pins on the main.

There are 4 ways to interpret the clock signal which need to be equal on both ends of a communication. This sometimes requires a reconfiguration of the interface when accessing different sub-devices on a single bus. Clock polarity determines whether the clock is high or low when idle. Clock phase determines whether the data needs to be valid on the first or the second edge.

Internally SPI interfaces are often implemented with a shift register on each side of the communication forming a virtual ring buffer.

Oftentimes subs use a simple protocol to allow read and write access to a memory region where the first byte in a transfer indicates the direction and memory address(max 7 bits). This is not part of the SPI standard and needs to be checked for every used sensor. Some may have an extra bit for multi-byte reads/writes.

#### 5.3 The Processing System and Python

written by Benjamin Bissendorf

Python is a programming language known for its accessibility to people new to programming and thus its large user base. There is a wide range of provided, community-supported modules enhancing the ecosystem.

The PYNQ-Z2 is a development board using features of the PYNQ framework by Xilinx. It is a Python-based development framework that allows the combination of normal Python programs and FPGA circuits to communicate. The board uses the ZYNQ XC7Z020-1CLG400C chip, which is a SoC that includes an ARM® Cortex®-A9 dual core processor and an FPGA. These subsystems are called the Processing System (PS) and the Programmable Logic (PL), respectively.

As Xilinx describes it, the power of this board is the combination of both the PS for standard tasks benefiting from an OS like communicating with USB-devices or communication via Ethernet, and the use of the PL for demanding or time-critical tasks [Adv22, cf.]. For interfacing between both systems, Xilinx provides the python package "pynq" that contains classes and functions to enable communication between these systems. For this, the "Overlay" class can be used, which dynamically loads a bitstream file into the FPGA and provides access to the design definitions such as AXI addresses. In the default operating system image, a Jupyter Notebook instance is included, enabling writing code via a web interface on the board and immediately starting the written code.

#### 5.4 Sensors

written by Benjamin Bissendorf

The ADXL312 is a 3-axis digital accelerometer sensor package made by Analog Devices. Its subsensors each consist of a spring-suspended structure, acting as a differential capacitor and thus providing values proportional to their acceleration. To fit a wide range of applications, the chip is highly configurable and allows different data-rates, -resolutions, -ranges (ranging from  $\pm 1, 5g$  up to  $\pm 12g$ ), and customizable data alignment. The sensor is able to measure the current acceleration up to 3200 times a second.

The onboard chip provides access to these settings and values via serial communication interfaces such as  $I^2C$  and SPI at predefined register addresses. For the used SPI communication, 3-wire and 4-wire configurations are supported while using the clock-phase = 1 and clock-polarity = 1 configuration. Have a look at its datasheet for an elaborate listing and explanation of the available registers (see [ADX22, page 19]).

Although not in the scope of this project, the chip offers different ways of saving power. While using lower data rates already reduces the chips' current substantially, it also offers an additional "low-power"-mode which can be enabled in special registers. This additionally reduces the drawn current by about 30% but comes with an increase in noise. This might be useful in projects where the amount of available power is limited.

#### 5.5 Actors

written by Niklas Seeliger

The camera platform is mounted on a central rod that is stiff enough to hold the platform in place when no other forces are enacted. It is however flexible enough that it can bend slightly which allows rotation of the entire platform. Mounted to the platform 90° from each other are rods connecting to actors that can push the platform up and down. Because the center is fixed in space by the rod in the middle, this causes rotation along one axis. The two actors can move the platform independently from each other in the two relevant axes.

These actors have to be able to move the platform very rapidly, that is with a high frequency, and with high precision but only a small distance. For those reasons, speakers were selected. Since speakers need to generate a very specific sound wave they have to move in a precise manner. Speakers are usually rated to generate all frequencies in the audible spectrum from 20Hz to 20kHz. This is more than enough to correct vibrations up to 1kHz. On the low end, it might even be enough to correct for some orbital movement, given the shutter speed is high enough. With the exception of the membrane that couples the actor to the air, the speakers are equivalent to a voice coil actuator. A mobile coil mounted around a static permanent magnet. When current passes through the coil the induced magnetic field interacts with that of the static magnet and the coil is moved linearly through a track it is mounted in.

Using speakers as the actors has the added benefit of being able to use dedicated audio hardware to generate analog signals. In the same vein, we can use standard equipment such as amplifiers and audio jacks. Since moving the platform simplifies to playing a sound we can make use of the on-board audio chip on our hardware. Using readily available hardware also lowers cost and development time.

Driving the audio signal is different from typical applications only in that we cannot buffer any audio data as that would introduce a significant delay to the feedback loop which would make the control loop significantly more difficult to impossible. Driving an analog signal from a digital System introduces some delay in the digital-to-analog conversion which we cannot avoid.

# Concept for the digital control system

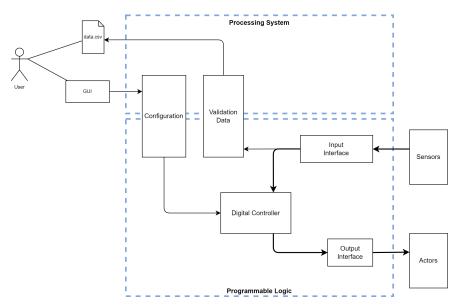

This section describes the general concept and structure of our solution.

In figure 6.1 you can see an overview of the components. Highlighted with thicker arrows, the main controlling path can be seen: The "Sensors" provide information about the acceleration of the contraption, which is polled by the "Input Interface". It combines the data into a single stream and pushes it into the "Validation Data" component and the "Digital Controller" component. The latter one uses this information to approximate the current deflection of each sensor and outputs counter-steering signals which are transformed and sent via the "Output interface" to the "Actors". For testing purposes, the user has the ability to either provide different controlling parameters for the "Digital Controller" via the "Configuration" component or read the past sensor readings which are written by the "Validation Data" component, written into a text file in the filesystem.

Figure 6.1: The structure of our concept for the digital control system

### 6.1 Configuration

written by Simon Pfennig

The Configuration Interface is used to send data from the PS to the PL. This can, for example, be used to adjust the parameters of the Controller during System Validation. For this purpose, the PS-General Purpose Input / Output (GPIO) Pins are used. These pins can be accessed from both PS and PL. In this project, a function, provided by the Jupyter-Notebook environment on the PS, is called to write data to an IP-Block which will hold the data in a register for further use by the PL.

#### 6.2 Input Interface

written by Joscha Knobloch

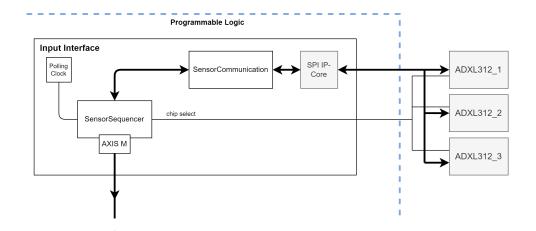

Figure 6.2: Internal structure of the Input Interface (BB)

The Input Interface is designated to retrieve data from the sensors and forward them to the "Validation Data" and "Digital Controller". The sensors are accessed by a common SPI Bus with individual chip select lines for each sensor. Externally a single AXI Stream interface can be used for the output as both the "Validation Data" and "Digital Controller" blocks need this interface.

Internally the Input Interface is broken up into a few blocks to reduce the complexity in any one block. The Polling Block is used to generate a clock signal for polling the sensor data. This is used by the SensorSequencer block, which controls the chip select lines and gives commands to the SensorComunication block. The commands are given by pulsing special specified lines and can be used to either configure a sensor or retrieve data from it.

The SensorCommunication block uses AXI4 Lite to communicate with the SPI IP-Core from Xilinx which then uses SPI to communicate with the sensors.

The SensorCommunication block does not control the chip select lines of the sensors. These will always be set accordingly by the SensorSequencer block, so the SensorCommunication block can communicate with the sensors with minimal extra logic. The SensorCommunication block is not aware that there are multiple sensors.

From the SensorCommunication towards the SensorSequencer, an AXI Stream interface is used as well.

## 6.3 Digital Controller

written by Janek Brumund

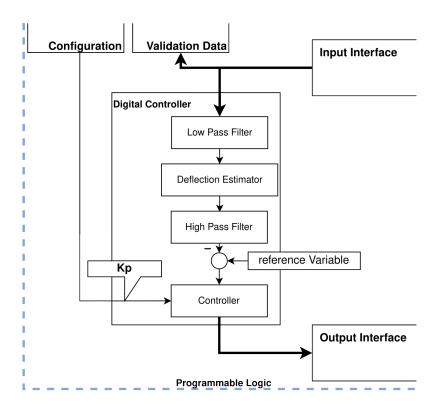

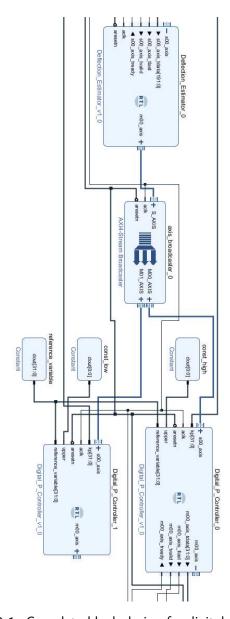

This section describes the concept for the Digital Controller unit. The following figure shows the detailed structure of the Controller (see Figure 6.3).

It consists of multiple components:

- Low Pass Filter

- Deflection Estimator

- High Pass Filter

- Controller

Figure 6.3: The structure of the concept for the digital controller

#### 6.3.1 Filters

The "Low Pass-" and "High Pass Filter" are digital filters. They will pass signals and signal components with a certain frequency. The **Low Pass** filter filters all signal components with a higher frequency as configured. Respectively, the **High Pass** filter filters all components till a certain frequency. Use cases for each filter are:

- "Low Pass Filter": preventing control of fast signals that would lead to errors

- "High Pass Filter": preventing control of slow signals that could not be processed by the actors

Each filter should be implemented using an Intellectual Property (IP) core called "FIR Compiler" (see [AMD22b]). Finite Impulse Response (FIR) filters are non-recursive filters which means that they are inherently stable [cf. EVN24, p.264]. They depend only on the current and previous input values.

#### 6.3.2 Deflection Estimator

The "Deflection Estimator" is used to calculate the current deflection of the platform. To do so, the measured acceleration is transformed. This is possible because the following equations (6.1 and 6.2) taken from [Men13, p.33] are valid:

$$s(t) = s_0 + v_0 t + \frac{1}{2} a t^2 = s_0 + \frac{1}{2} (v + v_0) t$$

(6.1)

$$v(t) = v_0 + at \tag{6.2}$$

The current velocity is calculated using the equation 6.2. With

$$v = at \text{ [cf. Men13, p.38]}$$

(6.3)

and equation 6.1 follows equation 6.4.

$$s(t) = s_0 + \frac{1}{2}v(t) \cdot t \tag{6.4}$$

The t in this equations is the sampling time  $t_a$  which is the inverse of the sampling frequency  $f_a$ .

$$t_a = \frac{1}{f_a}$$

As described in [ADX22] the measured acceleration will have a sensitivity of  $2,9\frac{mg}{LSB}$ . With

$$mg = g \cdot 10^{-3} = 9,81 \cdot 10^{-3} \frac{m}{s^2}$$

the unit for the acceleration a will be

$$[a] = 2,9 \frac{mg}{LSB} = 2,9 \cdot 9,81 \cdot 10^{-3} \frac{\frac{m}{s^2}}{LSB}$$

This means, one Least Significant Bit (LSB) represents  $2,9\cdot 9,81\cdot 10^{-3}\frac{m}{s^2}$ . With equation 6.3 and  $k=2,9\cdot 9,81\cdot 10^{-3}$  this leads to

$$[v] = [v_0] + [a] \cdot [t]$$

$$= k \frac{\frac{m}{s^2}}{LSB} \cdot s$$

$$= k \frac{\frac{m \cdot s}{s^2}}{LSB}$$

$$= \frac{\frac{m}{s}}{LSB}$$

The factor k is omitted because it has no influence on the unit. With  $s=\frac{1}{2}vt$  [cf. Men13, p.38] this lead to

$$[s] = \frac{1}{2} \cdot [v] \cdot [t]$$

$$= \frac{\frac{m}{s}}{LSB} \cdot s$$

$$= \frac{m}{LSB}$$

Like k,  $\frac{1}{2}$  has no effect on the unit. That's why this factor is eliminated.

In consultation with Professor Bredereke, the time for t is set to 1s. This is possible because the sampling time is constant and can be eliminated or set to 1s.

In figure 6.4 the location of all sensors is specified.

Figure 6.4: Top view of PCB - specification of sensor numbers

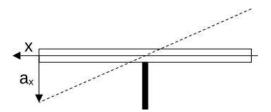

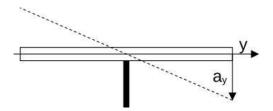

To determine the deflection on the x-axis the figure 6.5 serves as an illustration. The Printed Circuit Board (PCB) is shown in front view. Given a positive acceleration  $a_x$  the platform will be inclined to the left side. If a negative acceleration is given the platform tilts the other way around. This means there will be a positive deflection if the platform is inclined to the left.

Figure 6.5: Positive acceleration on x axis

The deflection on the y-axis is illustrated in figure 6.6. The PCB is shown in side view. If a positive acceleration  $a_y$  is given the platform will be inclined to the back. If a negative acceleration is given the platform tilts the other way around. This means there will be a positive deflection if the platform is inclined to the back.

Figure 6.6: Positive acceleration on y-axis

The measured and used acceleration is the acceleration from the z-axis of the sensors. The acceleration due to gravity is subtracted from acceleration on the axis. The result is the acceleration in the respective axis without the disturbance caused by the acceleration of gravity. This must be done because of the alignment of the platform. With this acceleration, the new deflection is calculated and this is added to the previous deflection. The result is the current deflection.

Ideas to determine the direction of deflection:

- 1. Calculate the difference between two acceleration values from different sensors.

- 2. Compare two acceleration values with  $g=9,81\frac{m}{s^2}$  and calculate the deflection with the value which

is higher than g acceleration after subtracting g. Depending on which sensor is used the result is either added or subtracted from the total deflection.

Example for the first idea:

$$\begin{split} a_x &= a_{x,0} - a_{x,1}, \text{ with } a_{x,0} = 0, 5\frac{m}{s^2} \text{ and } a_{x,1} = -0, 5\frac{m}{s^2} \\ &= 0, 5\frac{m}{s^2} - (-0, 5\frac{m}{s^2}) \\ &= 1\frac{m}{s^2} \end{split}$$

In this case, the result is twice as high as expected because both values were identical in amount. It is possible to divide the value by 2 to get the correct value. However, if the values are not the same in terms of amounts, it is no longer so easy. For this reason, we will work with the second idea.

#### 6.3.3 Controller

To generate a signal that could be used to control the actors, the "Controller" will be used. As mentioned earlier, we chose the PID controller to control the system. Since there is no standard and easy-to-use IP core for the PID controller, it was decided to implement only a P controller.

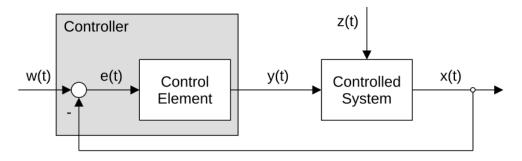

With respect to [Phi22] a controller is a module that gets the reference signal w(t) and substracts the controlled signal x(t) to generate the error signal e(t) (e(t) = w(t) - x(t)). The used control element takes the error signal and calculates the actuating signal y(t). The system could be affected by the disturbance signal z(t). Figure 6.7 shows this relation in a control loop.

Figure 6.7: Control loop - relations of the different signals

The control element could consist of multiple elements. A PID controller consists of a proportional (P), an integral (I), and a differential (D) component. According to [Phi22, p.132], the equation of time for this control element is equation 6.5.

$$y(t) = K_P e(t) + K_I \int_0^t e(t)dt + K_D \frac{de(t)}{dt}$$

(6.5)

To implement a PID controller the above equation must be implemented in PL. Because of the complexity of implementing this equation, the above decision (using P instead of PID controller) was made. It is also assumed that a P controller is sufficient, as the micro-vibrations of a constant speed of the motor are currently to be controlled. This assumption is made because it is assumed that a constant rotational speed results in a constant deflection of the platform.

The components for each element are:

- P: *K<sub>P</sub>e*(*t*)

- I:  $K_I \int_0^t e(t)dt$

• D:

$$K_D \frac{de(t)}{dt}$$

This means, that to implement a P controller the equation 6.6 must be implemented:

$$y(t) = K_P e(t), \text{ with } e(t) = w(t) - x(t)$$

(6.6)

Which is a multiplication of a (constant) factor  $K_P$  with the error signal.

Related to the previously described "Deflection Estimator", this means that the error signal is the current deflection of the platform.

#### 6.4 Output Interface

written by Niklas Seeliger

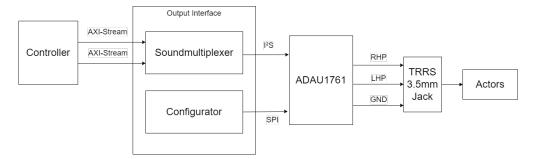

The output interface is responsible for taking a new state for the actors and sending it to the audio chip (an ADAU1761, data sheet is available online: [Ana10]) as digital audio data. There it is converted to an analog signal and is modulated to the the headphone jack output. From the controller, the interface should receive two AXI-Streams (one for each axis). The received data is buffered until it can be sent to the audio chip. A more detailed view of the Output-Interface and how it interfaces with surrounding components is shown in Figure 6.8.

The audio chip requires two lines of communication to work properly. It receives the audio data as an Inter Integrated Chip Sound (I<sup>2</sup>S) Stream. This stream contains both audio channels (referred to as left and right channels). The audio chip also needs to be configured. The audio chip has registers internally which need to be written to the desired configuration. This can be done either through an SPI or an I<sup>2</sup>C interface.

Figure 6.8: A detailed view of the output interface

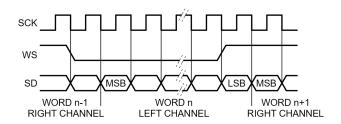

#### $6.4.1 I^2S$

$I^2S$  is a serial communication protocol designed for inter integrated chip sound data. The protocol is made up of two clock lines (serial clock, and word select line respectively) and one data line called serial data. The full specification is available online under [NXP22]. A brief summary is provided here.

The chip driving the serial clock and word select line is called the controller. The chip driving the serial data line is called the transmitter. The chip reading the serial data line is called the receiver. Either the transmitter or the receiver may the the controller (an external controller is also possible).

The **serial clock** line is the fastest clock in the interface. It is used to synchronize the bits of the audio data. With each rising clock edge a bit is read from the serial data line. The falling edges on this line are intended to trigger the next bit to be written to the serial data line by the transmitter. The data is transmitted in a twos complement format and can have any length of bits. Each word starts with the

Figure 6.9: I<sup>2</sup>S basic timing (Image taken from [NXP22])

most significant bit (the sign bit). This line is often referred to as the bitclock or BCLK line because it triggers the next bit.

The word select line is used to multiplex between different audio channels. In the simplest form, these are the left and the right audio channels. When the word select line goes to a logical 0 the left audio channel will be transmitted and when it goes to a logical 1 the right audio channel will be transmitted. This channel will be transmitted for as long as the word select line the value that corresponds to it. The value can only change with falling serial clock edges. After the word select advances to the next channel, the next bit that will be transmitted is the least significant bit of the previous channel. The transmission of the next most significant bit is delayed by 1 bitclock cycle. Figure 6.9 shows this delay. This line is often referred to as the left-right clock or LRCLK because it always alternates and triggers the transmission of the next channel.

The serial data line is the line on which the audio data is transmitted bit by bit. It is written during the falling edges of the serial clock and read on rising edges. It is not specified how many bits the audio data may be. The number of serial clock cycles for each word select channel may be shorter or longer than the serial data being transmitted. The transmitter therefore needs to be ready to change to the next word before the current word is fully transmitted. Likewise, it needs to be able to transmit more bits than the audio data has (for example by buffering with zeroes).

The serial clock frequency can be calculated with the data width and the sampling rate. For a sampling rate of 48kHz (typical for sound) and a data precision of 24 bit provided the word select allows for exactly the transmission of as many bits as are needed the serial clock frequency can be calculated as shown in Equation 6.7.

$$f_{sclk} = f_{sampling} \cdot precision \cdot 2$$

$$= 48 \ kHz \cdot 24 \cdot 2$$

$$= 2.304 \ MHz$$

(6.7)

#### 6.4.2 Configurator

The Configurator component is responsible for configuring the ADAU1761 chip. This includes general configuration such as enabling its clock as well as configuring the  $I^2S$  interface and modulating the received data to the headphone output that is used to interface with the actors. A detailed list of registers that need to be written can be seen in Appendix C. The configuration should be written immediately after a system reset. To configure the audio chip the SPI protocol was selected (as opposed to  $I^2C$ ) because it is used to read the sensors and because it offers much higher throughput than  $I^2C$ .

#### 6.4.3 Soundmultiplexer

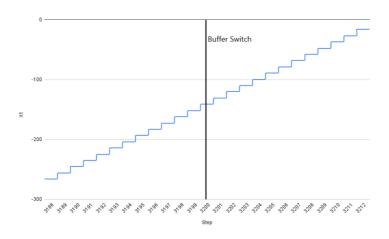

The sound multiplexer takes two AXI-Streams and outputs a time division multiplexed I<sup>2</sup>S stream. Since the throughput of the two AXI streams is far greater than the 48 kHz of the I<sup>2</sup>S Stream. Some values need to be discarded and cannot be sent to the audio chip. When a new I<sup>2</sup>S Word begins the last received data on that channel should be buffered to avoid data inconsistencies that might arise from changing

data while it is being serially sent over I²S to the audio chip. This introduces a time delay of at least 1 left-right clock cycle ( $1/48~kHz\approx20.83~\mu s$ ). This component should always be ready to receive data from the AXI Stream because the latest data should always be used to keep delay low. On the I²S side there is no reason to wait for the chip to be fully configured. The stream is valid even if the receiver has no knowledge of the last datum. Therefore no communication to the configuration component is required.

#### 6.5 Validation Data

#### written by Benjamin Bissendorf

For testing and validation purposes, the data provided by the sensors are to be recorded and written into a file in the file system, following a defined data structure to read it afterwards. This PL module is dependent on the data provided by the "Input Interface": Each time new data is available on the incoming stream, it is written to memory for the slower PS to collect and write into the filesystem.

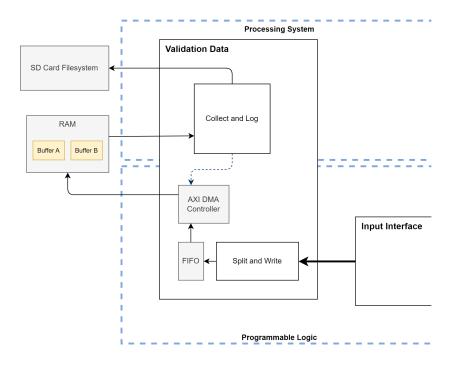

To achieve that, a combination of logic in the PL and the PS is used. An overview of the structure is given below in figure 6.10. The stream data, consisting of all the sensor data, is connected to a component splitting the data into 64 Bit chunks. Those are buffered and then written into memory. This data is extracted and the raw data is permanently written into a file, to be later postprocessed into a human and machine-readable CSV file. The details of implementation are documented in chapter 11.

Figure 6.10: A schematic of the internal structure of Validation Data

## Implementation of Input Interface

written by Joscha Knobloch

This section describes the implementation of the input interface which itself is composed of a few blocks as described in section 6.2 and visualised by image 6.2 on page 18. The blocks seen in the image are represented by individual blocks in the Vivado block design. The SPI core is provided by Xilinx. The SernsorCommunication block was started with the "Create and package new IP" Wizard in Vivado and is written in VHDL. The PollingClock- and SonsorSequencer blocks are written in VHDL as well.

#### 7.1 Sensor Communication

written by Joscha Knobloch

The SensorCommunication block connects to the SPI IP-Core via AXI Lite on the one side and the SensorSequencer block via AXI Stream on the other side.

Figure 7.1: Screenshot showing the custom Vivado IP core with its ports

The code is attached in the appendix. It consists of a top level file A.6 on page 78 and the main logic in a separate file A.7 on page 81.

Due to time constraints, this block is not finished and could therefore not be integrated into the overall solution for testing. However, simulations show that the AXI Lite interface is very likely working as expected. Due to tests done with Python as the AXI Master connected to the SPI IP-Core, the SPI functionality could also be shown working. As the SensorCommunication block is designed to use the same procedure on the AXI bus it is very likely that the SPI communication also works.

Therefore the only thing left would be to set up the specific sensor registers and acquire the sensor data. This should not be a very big task. Unfortunately, we could not finish it.

There is very little good information on how to use AXI Lite with VHDL on the internet. One could look up the details on the handshaking and implement the interface themselves. As the bus consists of five

independent channels with their own handshaking some sites recommend starting with the template that Vivado provides when using the "Create and package new IP" wizard for an AXI Lite Master core.

The provided template design is unfortunately not well documented and interwoven with an example that writes and then reads specific data to/from specified registers. It is very unclear how the template is supposed to be used. It specifies locations for "User logic", however, it is necessary to alter code outside of those areas to get the logic working at all. To make use of the provided code one needs to go through, understand every line of code, and then adapt it. This might be more work than implementing the interface from scratch.

In the concept phase of the project the SPI IP-Core was selected as AXI is the standard protocol to be used between IP-Cores. Due to the complexity of using AXI Lite it could have been easier to implement the SPI interface directly in VHDL.

For comprehensibility, the AXI Lite interface, the handling of the SPI-Core and the handling of the acceleration sensors are described separately.

#### 7.1.1 AXI Lite interface

The core contains one process per channel to facilitate the handshake. There are five channels in an AXI Lite bus as described in the theoretical background at section 5.1.1 on page 13. For channels going from the Master to the Slave, the valid flag needs to be set before the relevant clock cycle for the date to be read by the Slave. For the channels going from the Slave to the Master the ready flags need to be set to acknowledge the received data and signal the ability to receive data. These five processes were already present in the template, but some had to be modified heavily to be used for the general purpose.

There are also two processes for indicating a done read/write which were not present in the template. There is also a process that represents the AXI interface to the rest of the logic. It allows the next process to set a read/write bit, the address, and data if applicable, and then just trigger the transfer. A flag is pulsed high when the transfer is done and the results can be checked.

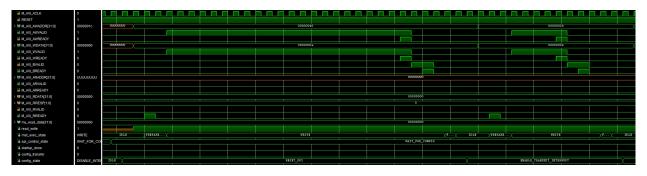

This part is very likely working as expected as it was tested in Vivado's simulator together with the SPI IP-Core. The handshake was visible and the response data made sense.

Figure 7.2: Screenshot showing the Vivado simulator with the AXI interface working

#### 7.1.2 Handling of the SPI Core by Xilinx

To use the Xilinx SPI IP-Core it needs to be configured at startup. This is done by a procedure of AXI transmissions. Therefore the core contains a process that can configure the SPI core and command it to do SPI transmissions when the relevant flags are set.

To configure the SPI core a flag for configuring is set, a line is given a pulse to start the procedure, and a done flag is waited for. When configuring the core, the process resets the SPI interface, enables the transmit interrupt, disables the global IPIF interrupt, deselects the slave, reads the control register, modifies some flags, and writes the control register.

To make an SPI transmission one must only set a flag for SPI transmission, set the data to send, start

the procedure, wait for the done flag to be set, and retrieve the received data. While the transmission is ongoing the process sets the data register, sets the slave register, reads the control register, modifies some flags, writes the control register, waits for the transmission to finish by checking the status register, and then deselects the slave.

This logic could not be tested due to time constraints. However, the process's behavior stems from a Python script by Marakena Labs which we were able to test with an acceleration sensor. Therefore it is also very likely that the SPI interface is working. [mat21]

#### 7.1.3 Handling of the acceleration sensors ADXL312

Finally, the acceleration sensors need to be accessed via SPI. In an earlier project stage, the ADXL355 sensor by analog devices was successfully sampled with the mentioned Python implementation for the SPI core. Due to time constraints, it was not possible to address the new sensor. To make it work it needs to be taken out of standby mode by setting some config registers. It can also be configured to use the smallest range of  $\pm 1.5g$  and sample at a given rate.

#### 7.2 Data Sequencer

written by Benjamin Bissendorf

The "Data Sequencer" is used to orchestrate the sensor configuration and sensor data retrieval process implemented by the "Sensor Communication" block.

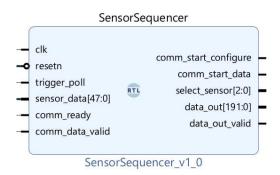

Its outer interfaces are depicted in figure 7.3 below. To specify the rate at which the data of all sensors should be polled, an external enable bit must be periodically provided into the  $trigger\_poll$  input. For the sensor configuration and data retrieval, the "Sensor Sequencer" is connected to the "Sensor Communication" block. For that, it uses the  $comm\_start\_configure$  flag to start configuring a sensor, while the  $comm\_start\_data$  flag is used to ask for the x-, y-, and z-axis data of one sensor. This data is returned into the  $sensor\_data$  line, accepting  $3 \cdot 16Bit = 48Bit$  of data. "Sensor Communication" can either signal that it and the sensors are configured with  $comm\_ready$  or it can signal that the requested data is available with the  $comm\_data\_ready$  flag. When the data of all sensors are ready, they are published to  $data\_out$  with the  $data\_out\_valid$  output set to '1'. The selection of which sensor is communicated with at the moment is the task of the Sequencer. For this the  $select\_sensor$  vector is provided to connect to the SPI chip select pins of the sensors.

Figure 7.3: The Sensor Sequencer block

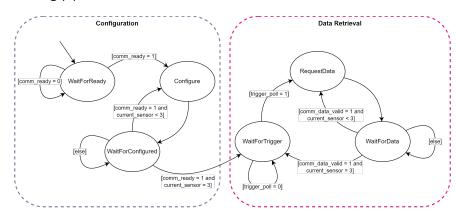

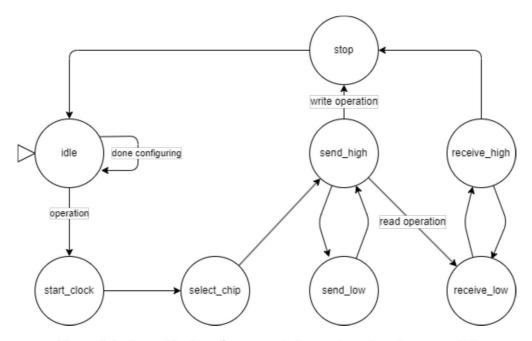

As one is familiar with the outer interfaces, the inner sequencing procedure is of interest. It was planned and implemented by following the deterministic finite state machine pattern, which can be seen in Figure 7.4. Generally, the block's sequence can be described by separating it into two parts: The configuration and the data retrieval.

After a system reset, the Sequencer waits for its counterpart, the "Sensor Communication", to be ready  $(comm\_ready = '1')$ , as it has to configure the blocks it is dependent on, like the AXI SPI Master. When

this is done, the sensors have to be configured (polling rate, data resolution, etc.). The Sequencer starts the configuration for each of the sensors after another by alternating between the states *Configure* and *WaitForConfigured* until all are done. Then the state machine transitions into the state *WaitForTrigger*, belonging to the "Data Retrieval" section. This section represents the group of states in the standard operation of polling the sensor data. The state machine always waits for the external polling clock to trigger a new polling cycle. When this happens, the state machine transitions into the *RequestData* state. There the "Sensor Communication" is signaled to get the data of the current sensor and another transition into *WaitForData* happens. There the Sequencer waits for the data to arrive and to save it into the *data\_out* vector. It transitions again to *RequestData* until all sensor data is collected. While transitioning from *WaitForData* to *WaitForTrigger*, the *data\_out\_valid* flag is set to start publishing the data into the following pipeline.

Figure 7.4: The finite state machine of the Data Sequencer

The complete VHDL implementation of this state machine can be seen in listing 9. A new VHDL type was defined consisting of the states in the previous diagram. Synchronous to the clock, states and their transition conditions are evaluated. One excerpt to point out can be found below in listing 1. It contains the definition of the transitions for the WaitForData state. When the sensor data is available, the incoming vector has to be written into a specific range of the output vector. The output vector is defined to have the sensor data in the order depicted in figure 7.5. As the sequencer polls  $Sensor\ 1$  first, its data has to be written into bits 191:144. This calculation is done in line 88 for  $current\_sensor \in [1,3]$ .

```

when WaitForData =>

84

comm_start_data <= '0';</pre>

86

if comm_data_valid = '1' then

87

buffer_upper_bits := 64*3 - 1 - 64*(current_sensor-1);

88

data_out(buffer_upper_bits downto

89

buffer_upper_bits - 16*3 + 1) <= sensor_data;</pre>

90

91

92

if current_sensor = 3 then

state <= WaitForTrigger;</pre>

93

data_out_valid <= '1';</pre>

94

95

else

state <= RequestData;</pre>

96

97

end if:

98

end if:

```

Listing 1: SensorSequencer.vhd for the Input Interface component

Visible in the figure of the data format below are the empty spaces as each sensor has a range of 64 Bits of data, while only 48 Bits are used for the three axes. This was done to pre-format the data for easier logging in the Validation Data component and to enable easier extensions in future iterations.

Figure 7.5: The data format of the outgoing stream

### 7.3 Polling Clock

written by Benjamin Bissendorf

As described in the previous section, the "Sensor Sequencer" needs an enable signal to indicate polling new data. The rate was determined to be 3200 times a second. The "Polling Clock" is the block implemented to reduce the incoming clock signal into a single enable output after a specified amount of ticks. As such, the outer interface is as simple as depicted in figure 7.6.

Figure 7.6: Our Clock Trigger block used as the Polling Clock

To calculate the number of ticks after which an enable signal has to be given, one has to know the system clock frequency and the polling frequency:

$$n_{ticks} = \frac{T_{poll}}{T_{clk}} = \frac{f_{clk}}{f_{poll}} = \frac{100.000.000Hz}{3200Hz} = 31.250$$

## 7.4 Sensor Dummy

written by Simon Pfennig

As the Input interface was not ready for integration with the other components, we decided to implement a Dummy Component (see Appendix 10) to emulate the sensor output for testing purposes. This component implements the interface with the Data Sequencer.

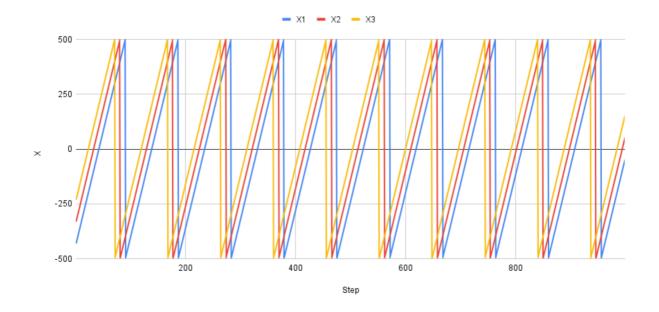

Internally it consists of three 16-bit counters which count from -500 to 500 and then reset. This implements a Sawtooth-Wave that can be sampled. The timespan, between each increase of the count can be configured and is independent of the polling from the Data Sequencer, as this aims to represent the actual variable that would be read by the sensor. Each of the counters can be initialized with a different offset, allowing a phaseshift between the signals.

The contents of the counters are exposed to the SensorData-Input of the Data Sequencer when it polls the data from the sensor Dummy. According to the SensorSelect-Signal one of the three counters will be used for that, simulating the request to different sensors. At this point, all three axes of a given simulated sensor show the same Sawtooth-Wave as output, since we only use one axis for testing.

# Implementation of Digital Controller

written by Janek Brumund

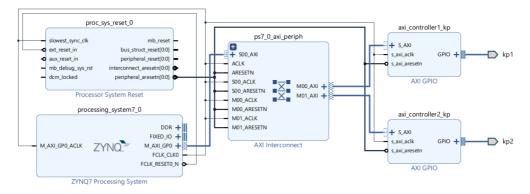

In this section, the implemented components are described. The complete block design is shown in Appendix D.1. There is the "Deflection\_Estimator" on the left side of this figure. This block takes the measured acceleration on an Advanced eXtensible Interface (AXI) Stream interface and determines the deflection of the x and y axis (see section 6.3.2). The calculated data is passed on to two "Digital\_P\_Controller" blocks through an "AXI4-Stream Broadcaster" Intellectual Property (IP) core. The controller blocks calculate the actuating signal depending on the given reference variable ("Constant" core) and a given factor for  $K_P$ . The  $K_P$  is given through another IP core called "AXI GPIO" (see chapter 10). To determine which half of the data is passed on from the "Deflection\_Estimator", two more "Constant" blocks are needed. One for a constant low level and one for a constant high level. The controller blocks pass the data to the "Output Interface" (see chapter 9).

#### 8.1 Filters

To implement a digital filter ("High Pass-" or "Low Pass Filter") the "FIR Compiler" IP core is used. It is a highly configurable core that can take one or multiple sets of coefficients. The coefficients for each filter are calculated using the "pyFDA" ([CHI24]) tool. With this tool, it is possible to calculate coefficients for different types of filters. Multiple data paths can be configured. The width of the input is also configurable. Besides that the type of the coefficients is configurable. For more information on how to configure such an IP core see [AMD22].

To keep the calculations simple these components are not included in the complete design. This decision was made because using numbers with decimal places as coefficients leads to output values with decimal places. This makes the calculations needed in "Deflection\_Estimator" and "Digital\_P\_Controller" more complex. To make it possible to solve the given problem in the given time the calculations must be easy enough to implement.

The designed filters could be reproduced using "pyFDA". All necessary files are available in the related repository on the GitLab server from the university.

#### 8.1.1 Low Pass Filter

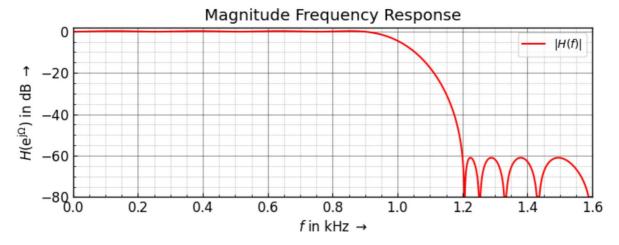

Figure 8.1 shows the response of the designed low pass filter. At  $f \approx 1.0kHz$  the magnitude is around -5 dB. Before that, the magnitude is higher than this level. This means signals with a f < 1.0kHz are almost unfiltered.

Figure 8.1: Design of Low Pass Filter with pyFDA

The coefficients for this filter are listed in table B.1. These coefficients are used in Vivado to generate the frequency response shown in the figure 8.2.

Figure 8.2: Magnitude in "Freq. Response" tab of the Low Pass "FIR Compiler"

The result of comparing the figures 8.1 and 8.2 is that the amplitude responses are almost the same. This means the developed filter should behave like a low pass filter.

#### 8.1.2 High Pass Filter

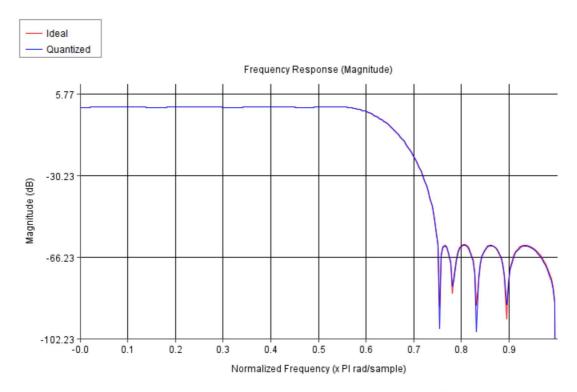

Figure 8.3 shows the designed high pass filter. At  $f\approx 50Hz$  the magnitude is -5 dB. With higher frequencies, the magnitude approaches 0 dB. This means signals with f>50Hz are almost unfiltered.

Figure 8.3: Design of High Pass Filter with pyFDA

The coefficients for this filter are listed in table B.1. These coefficients are used in Vivado to generate the frequency response shown in the figure 8.4.

Figure 8.4: Magnitude in "Freq. Response" tab of the High Pass "FIR Compiler"

The result of comparing the figures 8.3 and 8.4 is that the amplitude responses are almost the same. This means the developed filter should behave like a high pass filter.

#### 8.2 Deflection Estimator

The following section shows excerpts of the entire code in section A.4.

The "Deflection\_Estimator" gets its data through an AXI4-Stream slave interface. The data is then split according to the defined arrangement. In the calculation phase, the old values are first saved (see listing 2).

```

pre_x_deflection := x_deflection;

pre_y_deflection := y_deflection;

pre_x_velocity := x_velocity;

pre_y_velocity := y_velocity;

```

Listing 2: Save previous values

After that, the new acceleration values are compared to the gravitational acceleration. Afterward, the current acceleration is calculated for the axis by subtracting the gravitational acceleration. This value is used to calculate the current velocity for the axis. The current velocity is then used to calculate the current deflection for the axis.

```

if (z0_input_data > G_ACCEL and z1_input_data < G_ACCEL) then</pre>

1

-- left inclination

2

x_cur_accel := std_logic_vector(signed(z0_input_data) - signed(G_ACCEL));

3

x_velocity := std_logic_vector(signed(pre_x_velocity) + signed(x_cur_accel));

4

elsif (z0_input_data < G_ACCEL and z1_input_data > G_ACCEL) then

5

6

-- right inclination

x_cur_accel := std_logic_vector(signed(z1_input_data) - signed(G_ACCEL));

x_velocity := std_logic_vector(signed(pre_x_velocity) - signed(x_cur_accel));

8

9

else

10

-- no inclination

x_cur_accel := (others => '0');

11

x_velocity := std_logic_vector(signed(pre_x_velocity) + signed(x_cur_accel));

12

end if;

13

14

x_deflection <= std_logic_vector(signed(pre_x_deflection) + signed(x_velocity));</pre>

15

```

Listing 3: Calculate values for x axis

The calculation for the y-axis looks similar, which is why it was omitted.

Afterward, the values for the deflection on each axis are passed on to the output. The output is an AXI4-Stream master interface.

#### 8.3 Controller

The "Digital\_P\_Controller" gets the data via an AXI4-Stream Slave interface and picks one half of this. This is determined by the "upper" port. The following is an excerpt of the complete "Digital\_P\_Controller" code in section A.5.

The data goes through the calculations shown in listing 4. First, the difference between "reference\_variable" and "input data" is calculated. Then this value is multiplied by the given factor "kp".

```

puffer := signed(reference_variable) - signed(input_data);

calculated_data <= std_logic_vector(signed(kp) * puffer);</pre>

```

Listing 4: Calculate the current error signal and the actuating signal

After the calculation is done, the calculated data is passed on to the output. The output is an AXI4-Stream Master interface.

# Implementation of Output Interface

written by Niklas Seeliger

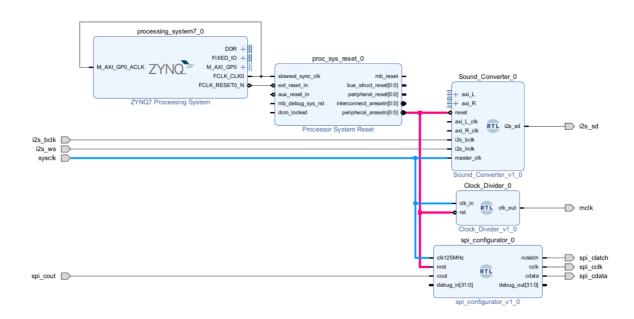

The output interface is made up of components. The configurator which upon getting a reset signal configures the audio chip and the Soundmultiplexer, which receives AXI-Streams and multiplexes them into an  $I^2S$  Stream that it sends to the audio chip.

### 9.1 ADAU1761 Operation

We want to use the audio chip to receive I<sup>2</sup>S data and drive the left and right headphone outputs to the levels of those channels. The headphone outputs of the chip are already hardwired to the "HP+Mic" labeled audio jack. However, the input side needs to be mapped to FPGA signals. We want to drive the headphone output with a sampling frequency of 48~kHz and want to operate the chip with a master clock of 256 times that (= 12.288~MHz).

The audio chip will be configured to be the Inter Integrated Chip Sound (I<sup>2</sup>S) controller and as such the serial clock and word select lines are inputs on the Field Programmable Gate Array which is programmed to transmit the audio data.

Checking the datasheet [Ana10] we need to interface with the following pins: