Hochschule Bremen

Fakultät 4: Elektrotechnik und Informatik

# **Konzeption und Entwicklung eines autonomen Vehikels mit Bild- und Sprachkommandoerkennung durch neuronale Netze auf einem weltraumtauglichen FPGA**

Keno Albers, Milan Becker, Luca Bianchi, Julius Böttger, Jan Bredereke,

Jonas Broda, Arian Dannemann, Frederic Goretzky, Jannik Hennicke,

Philipp Hennken, Alexander Hoegen-Jupp, Tim Jaeschke, Tuanna Karadas,

Nils Karsten, Jonas Kleimann, Simon Koger, Simon Köhler, Jonas Landwehr,

Kevin Lingk, Matthias Löwen, Marvin Lünswilken, Kilian Müller, Niklas Otten,

Enrico Ramm, Tim Ranft, Max Tepe, Nils van Rijsinge

Dozent: Prof. Dr. Jan Bredereke

Wir untersuchen, wie man neuronale Netze auf feldprogrammierbaren Gate-Arrays (FPGAs) am besten nutzen kann, wenn diese so leistungsbeschränkt wie strahlungsfeste FPGAs in der Raumfahrt sein müssen (und etwas allgemeiner entsprechend neuronale Netze auf FPGAs für Edge-Computing). Ein autonomes Modellauto als konkretes Vehikel dient uns dabei als Stellvertreter für ein autonomes Raumfahrzeug. An der Architektur, Hardware und Software dafür haben wir vieles verbessert. Darüber hinaus gibt eine Literaturrecherche zu Hardware-bedingten Rechenfehlern in neuronalen Netzen, motiviert durch die Problematik der Weltraumstrahlung, einen Überblick über die aktuelle Forschung zu schaltungstechnischen Maßnahmen zur Eindämmung der Fehlerwirkungen sowie zu Meßansätzen, um den Erfolg solcher Maßnahmen nachzuweisen. Und die experimentelle Untersuchung systematischer Fehler beim Erkennen von Sprachkommandos er gab Einsichten, worauf beim Training eines neuronalen Netzes dafür zu achten ist. Schließlich identifizieren wir interessante verbliebene Aufgaben und Herausforderungen im Kontext unserer Forschungsfrage.

# Inhaltsverzeichnis

|                                                                                                  |           |

|--------------------------------------------------------------------------------------------------|-----------|

| <b>1. Einleitung</b>                                                                             | <b>1</b>  |

| 1.1. Kontext . . . . .                                                                           | 1         |

| 1.2. Forschungsfrage . . . . .                                                                   | 2         |

| 1.3. Die Beispielanwendung . . . . .                                                             | 2         |

| 1.4. Vorhergehende Arbeiten an der Hochschule Bremen . . . . .                                   | 2         |

| 1.4.1. Bilderkennung . . . . .                                                                   | 2         |

| 1.4.2. Sprachkommandoerkennung . . . . .                                                         | 3         |

| 1.5. Behandelte Teilthemen in der aktuellen Runde des Projekts . . . . .                         | 3         |

| <b>2. Überblick über die Systemarchitektur</b>                                                   | <b>5</b>  |

| 2.1. Vorherige Ergebnisse . . . . .                                                              | 5         |

| 2.2. Datenaustausch zwischen PS und PL . . . . .                                                 | 7         |

| 2.2.1. AXI (Advanced Extensible Interface) . . . . .                                             | 8         |

| 2.2.2. Datentransfer zwischen Processing System und neuronalen Netz . . . . .                    | 8         |

| 2.2.3. Verwendete Hilfsquellen zum Verständnis der Projektarchitektur . . . . .                  | 8         |

| 2.3. Geplante Architektur . . . . .                                                              | 9         |

| 2.3.1. Personen- und Gestenerkennung . . . . .                                                   | 9         |

| 2.3.2. Spracherkennung . . . . .                                                                 | 10        |

| 2.3.3. Fahrzeug- und Motorsteuerung . . . . .                                                    | 10        |

| <b>3. Personenerkennung</b>                                                                      | <b>13</b> |

| 3.1. Behandelte Themen . . . . .                                                                 | 13        |

| 3.2. Grundlagen . . . . .                                                                        | 13        |

| 3.2.1. Overfitting . . . . .                                                                     | 13        |

| 3.2.2. Stratified Sampling . . . . .                                                             | 14        |

| 3.2.3. Trainieren von neuronalen Netzen und Modellbewertung . . . . .                            | 14        |

| 3.3. Erkenntnisse aus vorherigen Projektberichten . . . . .                                      | 15        |

| 3.4. Bisheriger Stand des Codes . . . . .                                                        | 16        |

| 3.4.1. Bisheriger Stand und Probleme des Trainingsskripts . . . . .                              | 17        |

| 3.4.2. Bisheriger Stand und Probleme des Testskripts . . . . .                                   | 17        |

| 3.4.3. Durchführen des Trainings- und Testverfahrens mit bestehendem Modell und Skript . . . . . | 18        |

---

|                                                                               |           |

|-------------------------------------------------------------------------------|-----------|

| 3.5. Verbesserungen . . . . .                                                 | 19        |

| 3.5.1. Allgemeine Verbesserungen . . . . .                                    | 19        |

| 3.5.2. Verbesserungen für eine reproduzierbare Entwicklungsumgebung . . . . . | 20        |

| 3.5.3. Trainingsskript Verbesserung . . . . .                                 | 21        |

| 3.5.4. Testskript Verbesserung . . . . .                                      | 23        |

| 3.5.5. Erweiterung des Datensatzes . . . . .                                  | 25        |

| 3.6. Formalisierung einer Testmethode . . . . .                               | 25        |

| 3.6.1. Vorgehen und Hintergrund . . . . .                                     | 25        |

| 3.6.2. Test . . . . .                                                         | 27        |

| 3.7. Zusammenfassung und Fazit . . . . .                                      | 31        |

| 3.8. Ausblick . . . . .                                                       | 32        |

| <b>4. Gestenerkennung</b> . . . . .                                           | <b>33</b> |

| 4.1. Einführung und Problembeschreibung . . . . .                             | 33        |

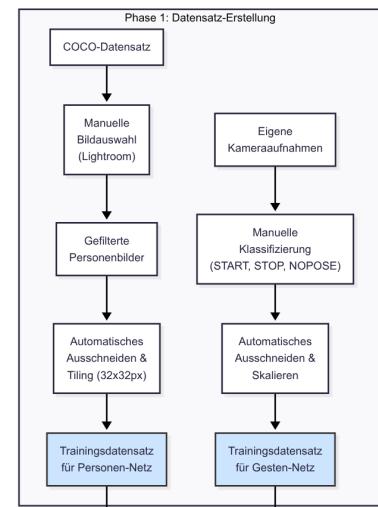

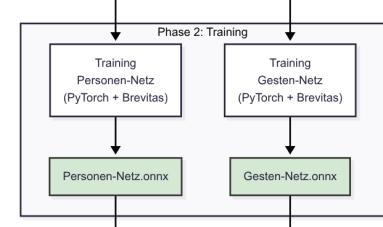

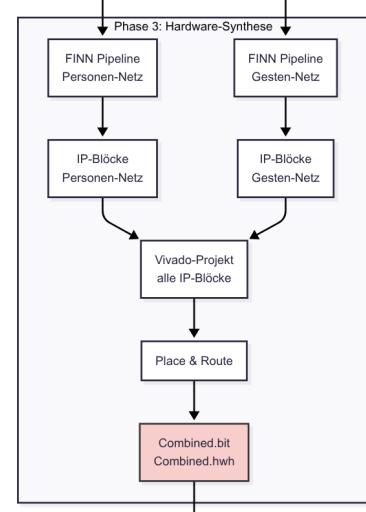

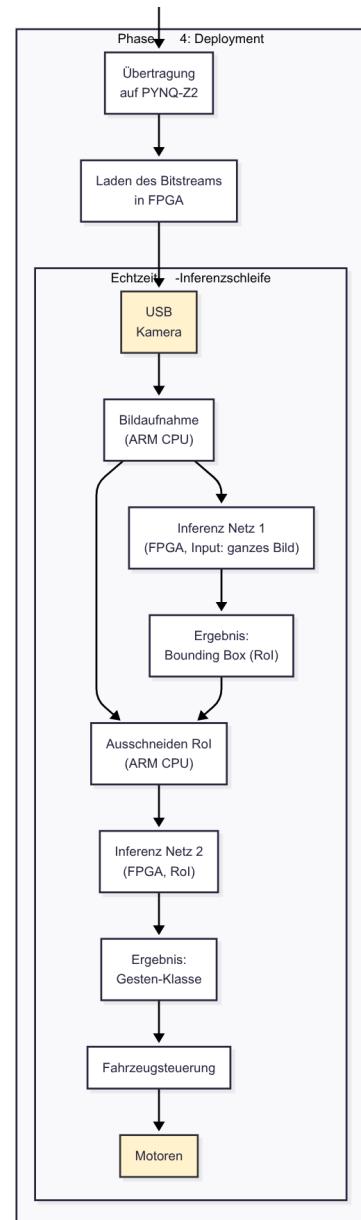

| 4.2. Systemübersicht Personen-/Gestenerkennung . . . . .                      | 34        |

| 4.3. Bisheriger Stand und identifizierte Probleme . . . . .                   | 36        |

| 4.3.1. Datengrundlage . . . . .                                               | 36        |

| 4.3.2. Ressourcenlimit des FPGA & Optimierungsstrategien . . . . .            | 37        |

| 4.3.3. Training . . . . .                                                     | 37        |

| 4.3.4. Hardwaresynthese . . . . .                                             | 38        |

| 4.3.5. Deployment . . . . .                                                   | 38        |

| 4.3.6. Integration . . . . .                                                  | 38        |

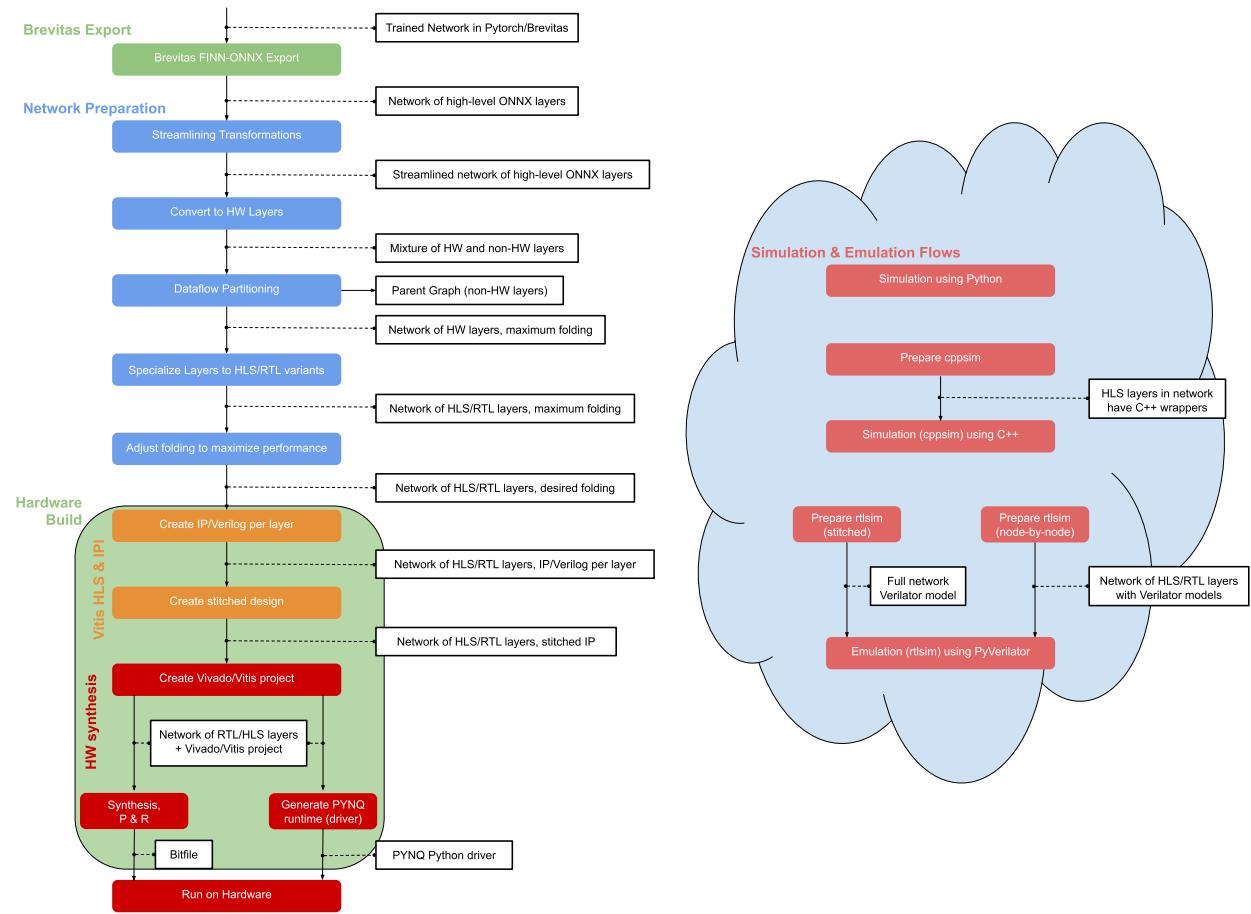

| 4.4. FINN Toolchain . . . . .                                                 | 39        |

| 4.4.1. Einrichtung von FINN . . . . .                                         | 40        |

| 4.4.2. Weiterführende Links zur FINN-Toolchain . . . . .                      | 41        |

| 4.5. Yolo („You Only Look Once“) . . . . .                                    | 42        |

| 4.5.1. Training . . . . .                                                     | 42        |

| 4.5.2. Deployment . . . . .                                                   | 43        |

| 4.5.3. Alternative Deployment-Möglichkeiten für YOLO mit FINN . . . . .       | 43        |

| 4.6. Alternative Ansätze . . . . .                                            | 44        |

| 4.6.1. Vitis AI . . . . .                                                     | 44        |

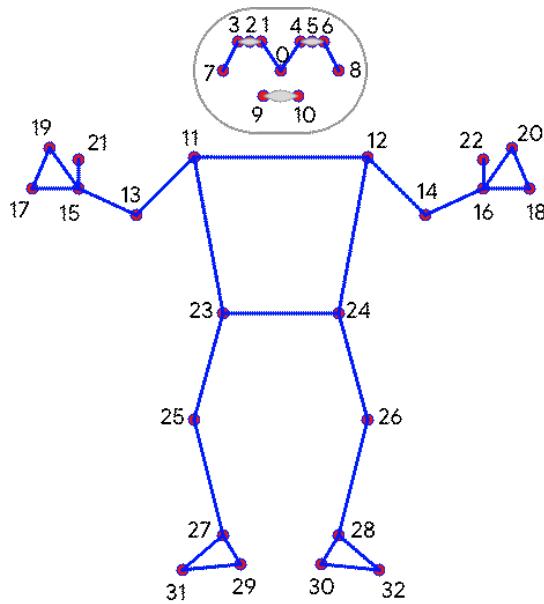

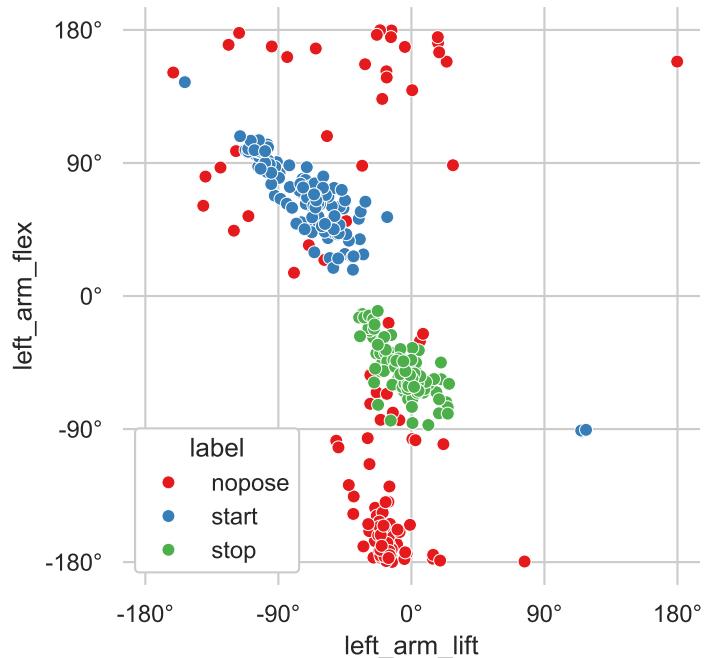

| 4.6.2. Pose Landmark Detection . . . . .                                      | 44        |

| 4.6.3. Kombinierte Personen- und Gestenerkennung . . . . .                    | 47        |

|                                                                                     |           |

|-------------------------------------------------------------------------------------|-----------|

| 4.7. Ausblick . . . . .                                                             | 49        |

| 4.7.1. Vervollständigung der FPGA-basierten Inferenzkette . . . . .                 | 49        |

| 4.7.2. Automatisierung der Toolchain und Build-Prozesse . . . . .                   | 50        |

| 4.7.3. Evaluation alternativer Gestenerkennungsverfahren . . . . .                  | 50        |

| <b>5. Fahrsteuerung</b> . . . . .                                                   | <b>51</b> |

| 5.1. Grundlagen . . . . .                                                           | 51        |

| 5.1.1. Speicherort und Ausführung der Anwendung . . . . .                           | 51        |

| 5.1.2. PDM . . . . .                                                                | 51        |

| 5.2. Erkenntnisse aus vorherigen Projektberichten . . . . .                         | 56        |

| 5.2.1. Umsetzung der Fahrsteuerung . . . . .                                        | 56        |

| 5.2.2. Probleme bei der Geradeausfahrt . . . . .                                    | 56        |

| 5.2.3. Regulierung der Geschwindigkeit . . . . .                                    | 57        |

| 5.3. Erarbeitete Ergebnisse . . . . .                                               | 57        |

| 5.3.1. Versuch zur Quantifizierung der Abweichung bei Geradeausfahrt . . . . .      | 58        |

| 5.3.2. Einrichtung und Verbindung eines AP . . . . .                                | 60        |

| 5.3.3. Konzept für Modularisierung der Fahrsteuerung . . . . .                      | 60        |

| 5.3.4. Ansteuerung des PYNQ-Z2 Boards . . . . .                                     | 61        |

| 5.3.5. Fahrsteuerung der Vorgruppe auf dem Z2-Board zum Laufen bringen . . . . .    | 62        |

| 5.3.6. Neu-Implementation der Fahrsteuerung in Python . . . . .                     | 62        |

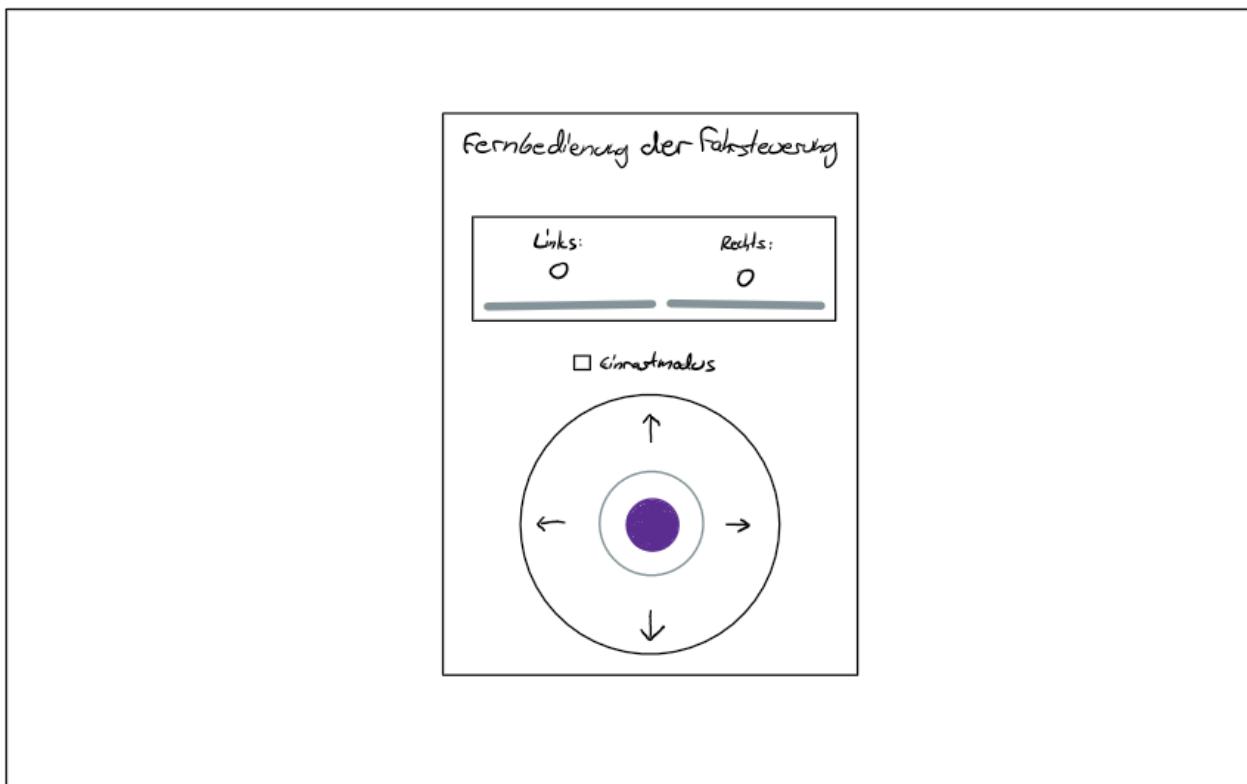

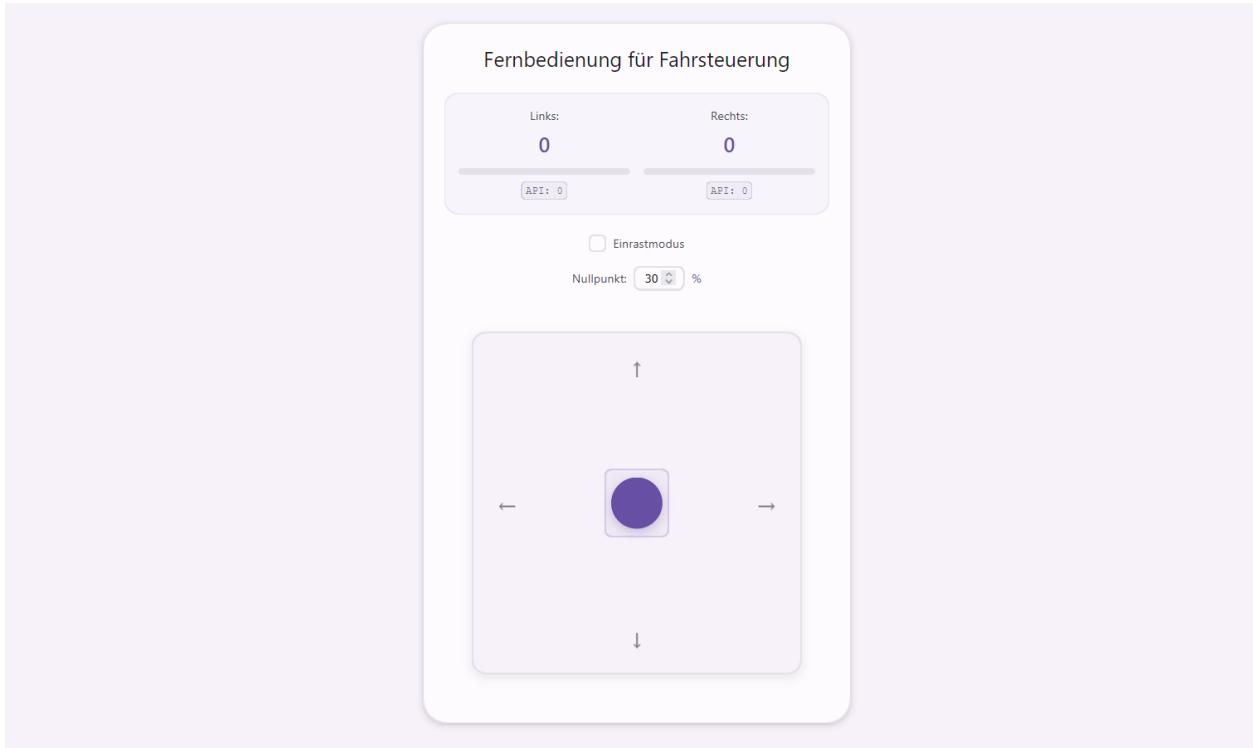

| 5.3.7. Benutzeroberfläche zur Steuerung . . . . .                                   | 63        |

| 5.4. Nächste Schritte . . . . .                                                     | 68        |

| 5.4.1. Integration der Fahrsteuerung parallel zu anderen Schaltungsteilen . . . . . | 68        |

| 5.4.2. Optimierung der Geradeausfahrt . . . . .                                     | 69        |

| 5.4.3. Neue Endpunkte für den Server . . . . .                                      | 69        |

| <b>6. Evaluation des neuen Mikrofons</b> . . . . .                                  | <b>70</b> |

| <b>7. Audioerkennung per neuronalem Netz</b> . . . . .                              | <b>75</b> |

| 7.1. Grundlagen . . . . .                                                           | 75        |

| 7.1.1. Neuronale Netze . . . . .                                                    | 75        |

| 7.1.2. Mono und Stereo Sound . . . . .                                              | 76        |

| 7.2. Ausgangssituation/ Bisherige Ergebnisse . . . . .                              | 77        |

---

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| 7.3. Untersuchung der Ursache für niedrige Erkennungsraten . . . . .   | 77        |

| 7.3.1. Korrektes Audio-Format . . . . .                                | 77        |

| 7.3.2. Laute Hintergrundgeräusche . . . . .                            | 79        |

| 7.3.3. Modell auf eine Stimmlage übertrainiert . . . . .               | 79        |

| 7.3.4. Positionierung des Kommandos innerhalb der Aufnahme . . . . .   | 80        |

| 7.3.5. Hintergrundrauschen bei langer Aufnahme . . . . .               | 81        |

| 7.3.6. Schlussfolgerung . . . . .                                      | 82        |

| 7.4. Filterung des Audiosignals . . . . .                              | 82        |

| 7.5. Ausblick . . . . .                                                | 83        |

| 7.5.1. Anpassung des Paddings . . . . .                                | 83        |

| 7.5.2. Implementierung eines Sliding Windows . . . . .                 | 83        |

| 7.5.3. Implementierung einer Spracherkennung . . . . .                 | 84        |

| <b>8. Elektronik und Mechanik</b>                                      | <b>85</b> |

| 8.1. Ausgangssituation . . . . .                                       | 85        |

| 8.2. Modifikation . . . . .                                            | 86        |

| 8.2.1. Adapterplatte . . . . .                                         | 86        |

| 8.2.2. Gehäuseoberteil . . . . .                                       | 87        |

| 8.2.3. Kameraaufnahme . . . . .                                        | 87        |

| 8.2.4. Mikrofonhalterung . . . . .                                     | 87        |

| 8.2.5. Fertigung und Materialwahl . . . . .                            | 87        |

| 8.2.6. Weitere Verbesserungen der bestehenden Hardware . . . . .       | 88        |

| 8.3. Materialliste des Gesamtfahrzeugs . . . . .                       | 89        |

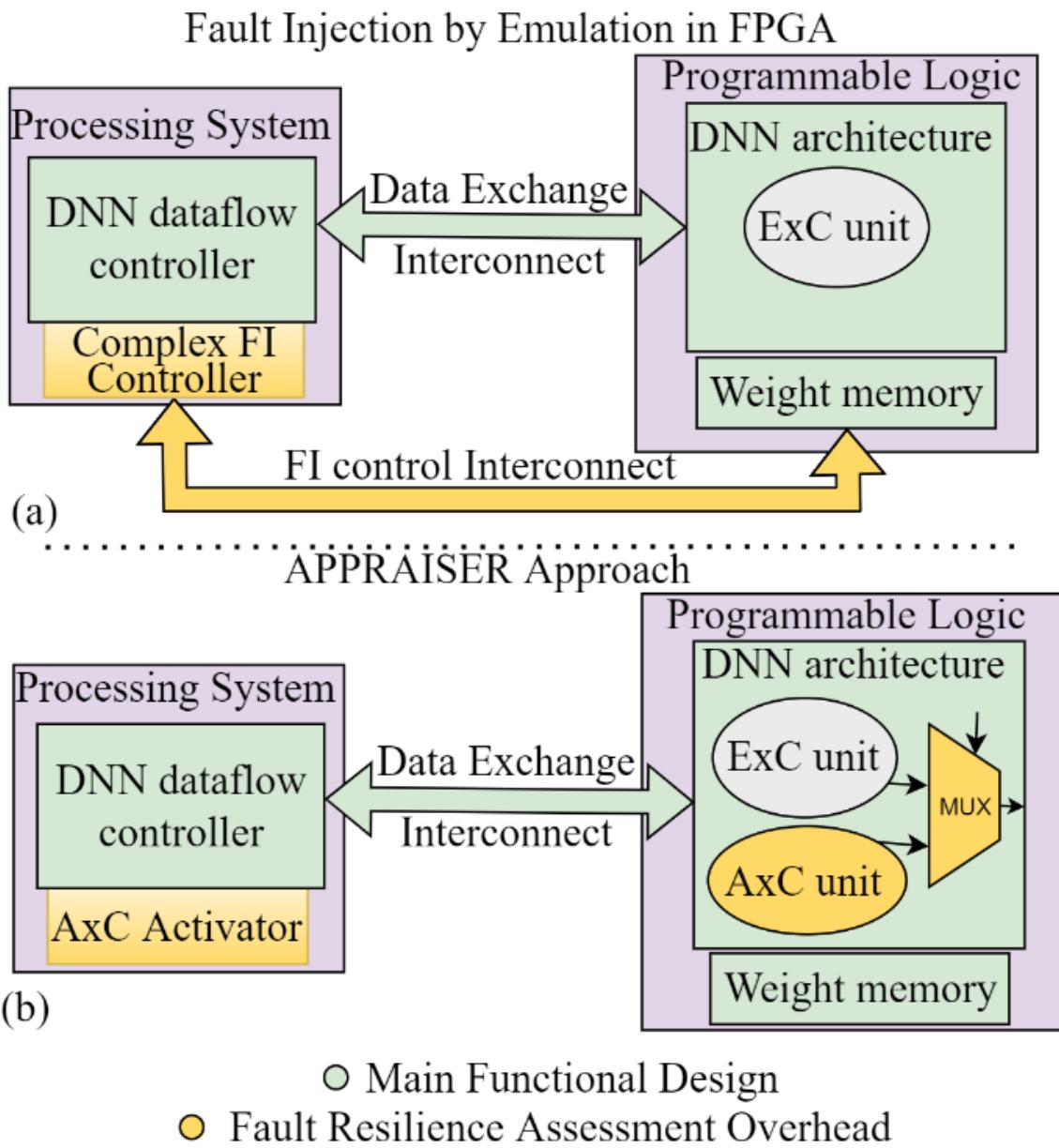

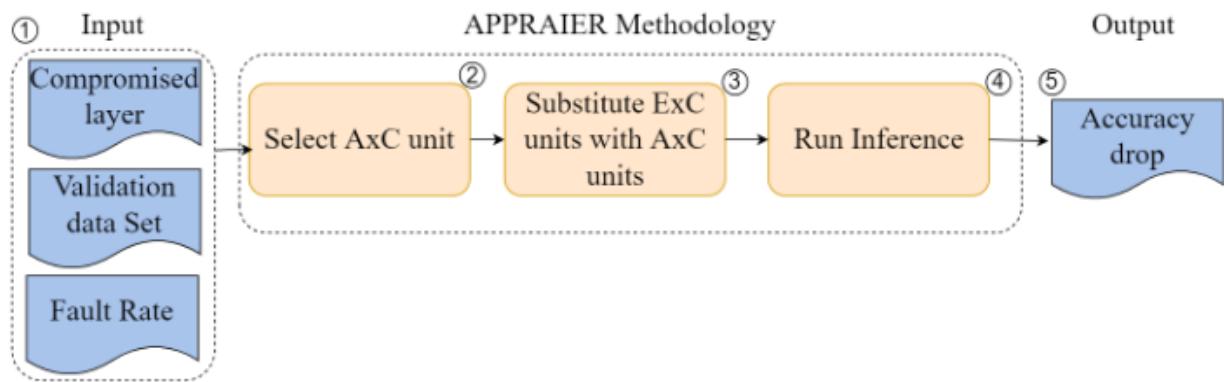

| <b>9. Auswirkungen von Rechenfehlern im neuronalen Netz abschätzen</b> | <b>91</b> |

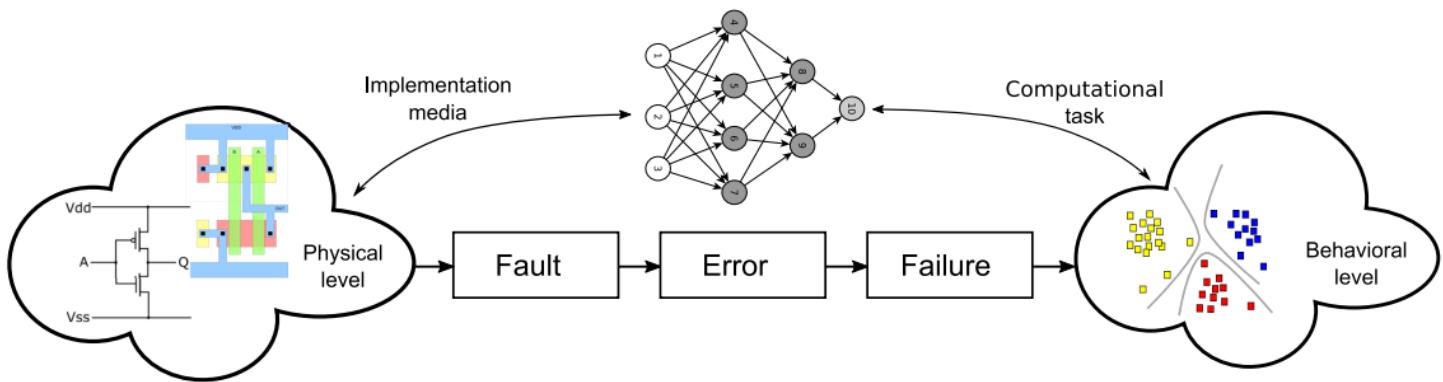

| 9.1. Einleitung . . . . .                                              | 91        |

| 9.1.1. Neuronale Netze . . . . .                                       | 91        |

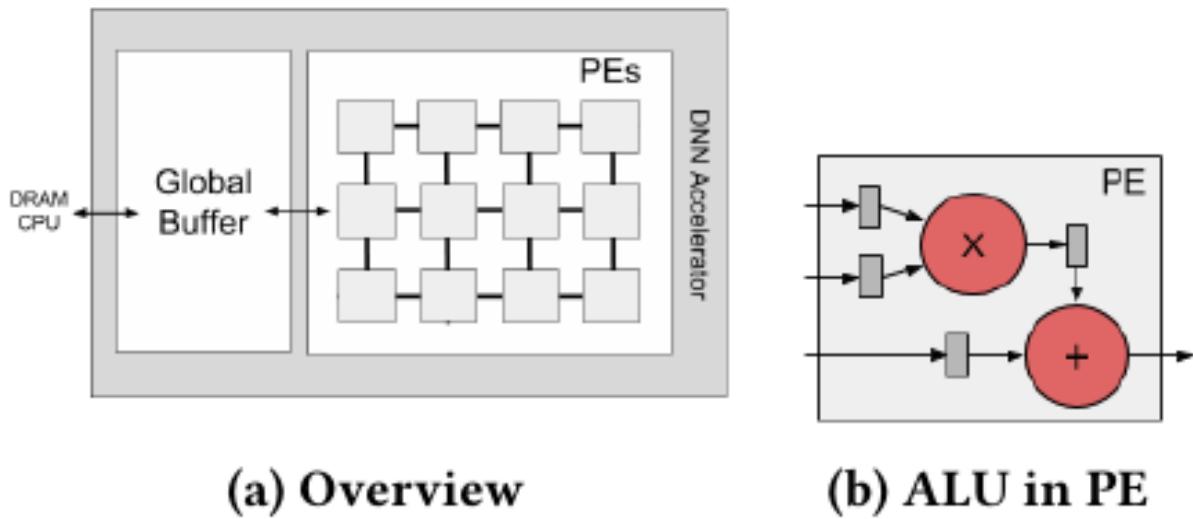

| 9.1.2. Beschleuniger . . . . .                                         | 91        |

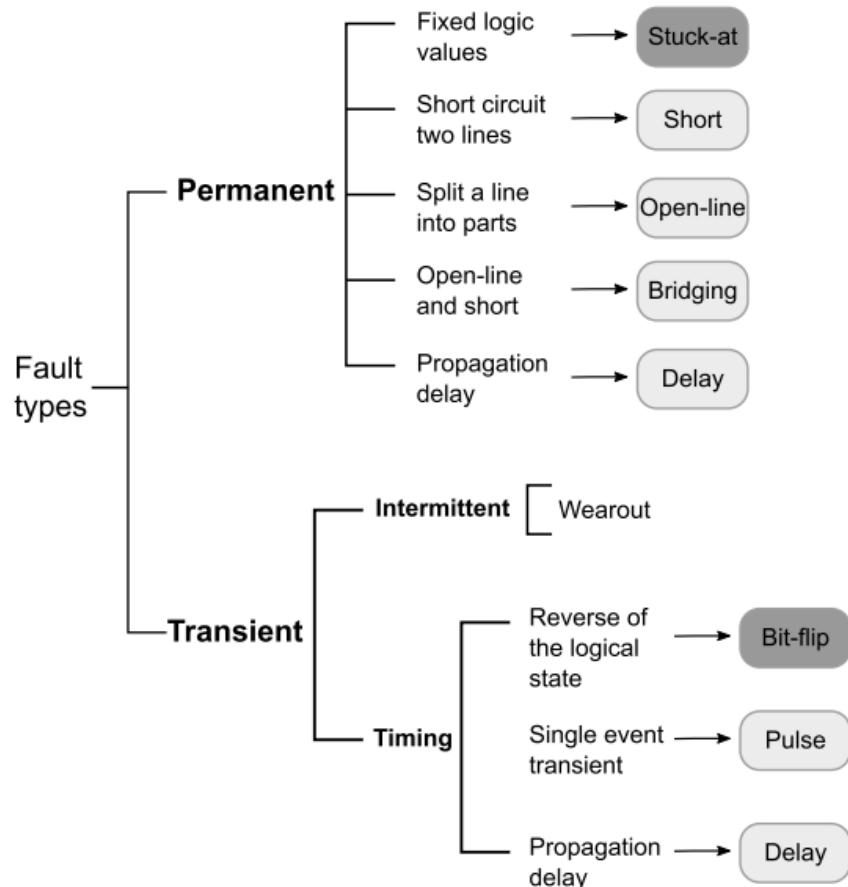

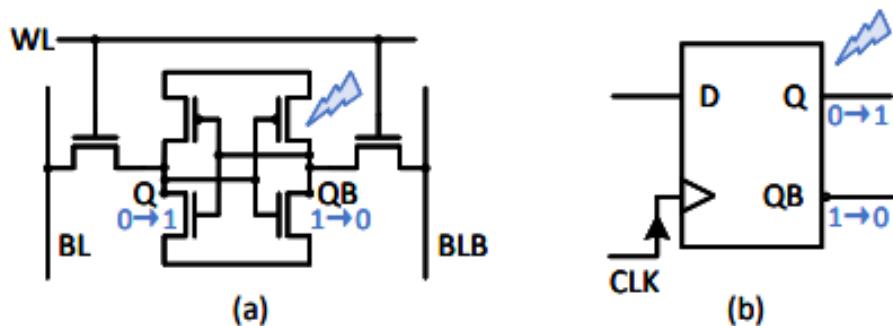

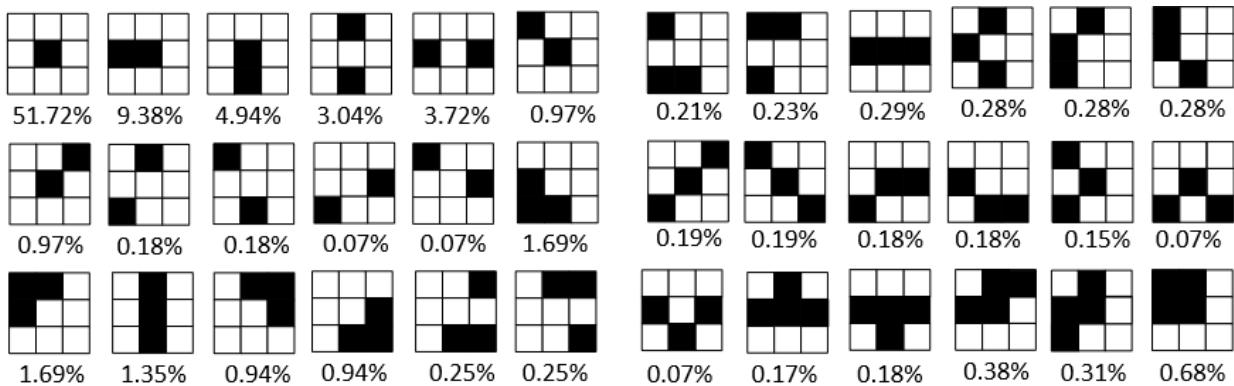

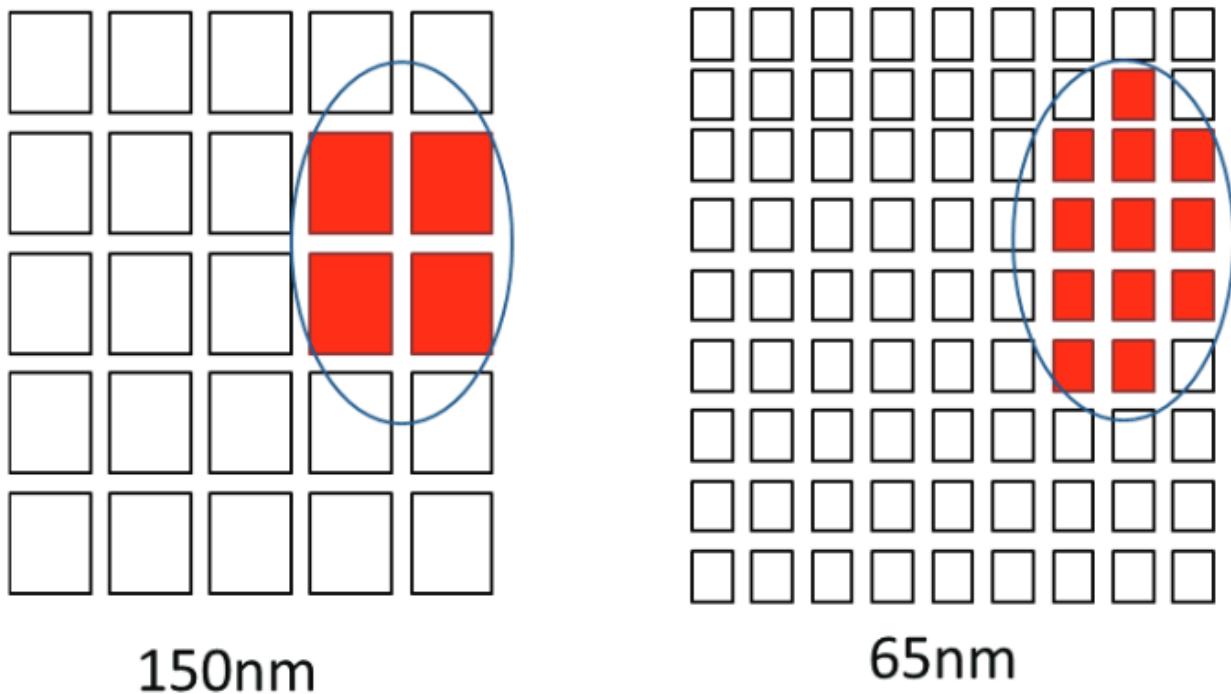

| 9.1.3. Relevante Fehlerarten . . . . .                                 | 92        |

| 9.1.4. Herausforderungen bei sicherheitsrelevanten Systemen . . . . .  | 98        |

| 9.2. Relevante Faktoren für Fehler . . . . .                           | 100       |

| 9.2.1. Physikalische Fehlerarten . . . . .                             | 101       |

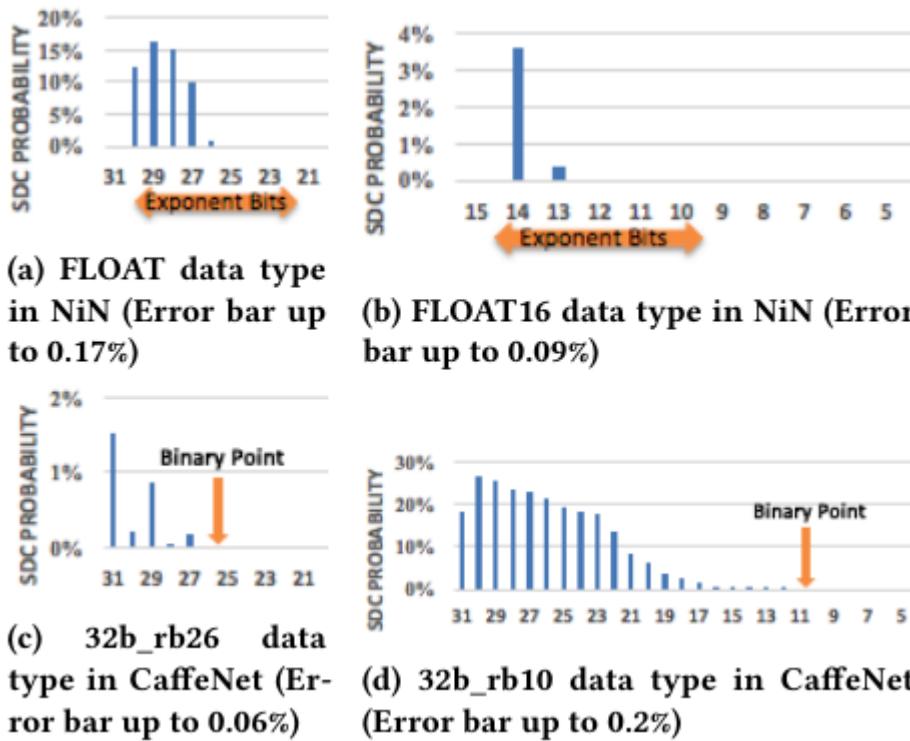

| 9.2.2. Bitbreite . . . . .                                             | 102       |

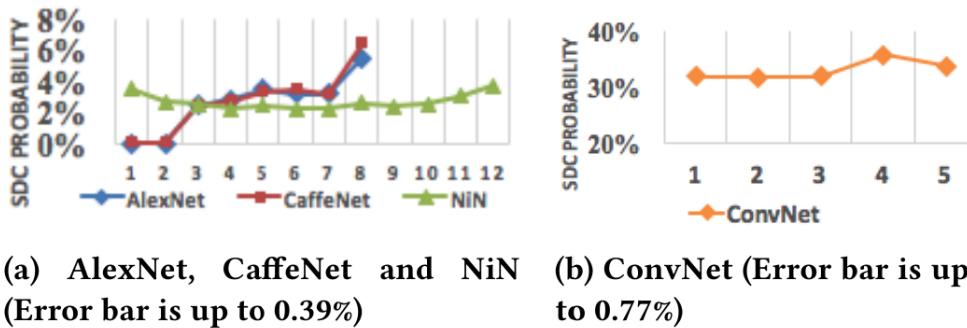

| 9.2.3. Topologie . . . . .                                             | 104       |

|                                                                             |            |

|-----------------------------------------------------------------------------|------------|

| 9.2.4. Bitposition . . . . .                                                | 105        |

| 9.2.5. Flip-Richtung . . . . .                                              | 106        |

| 9.3. Auswirkungen . . . . .                                                 | 107        |

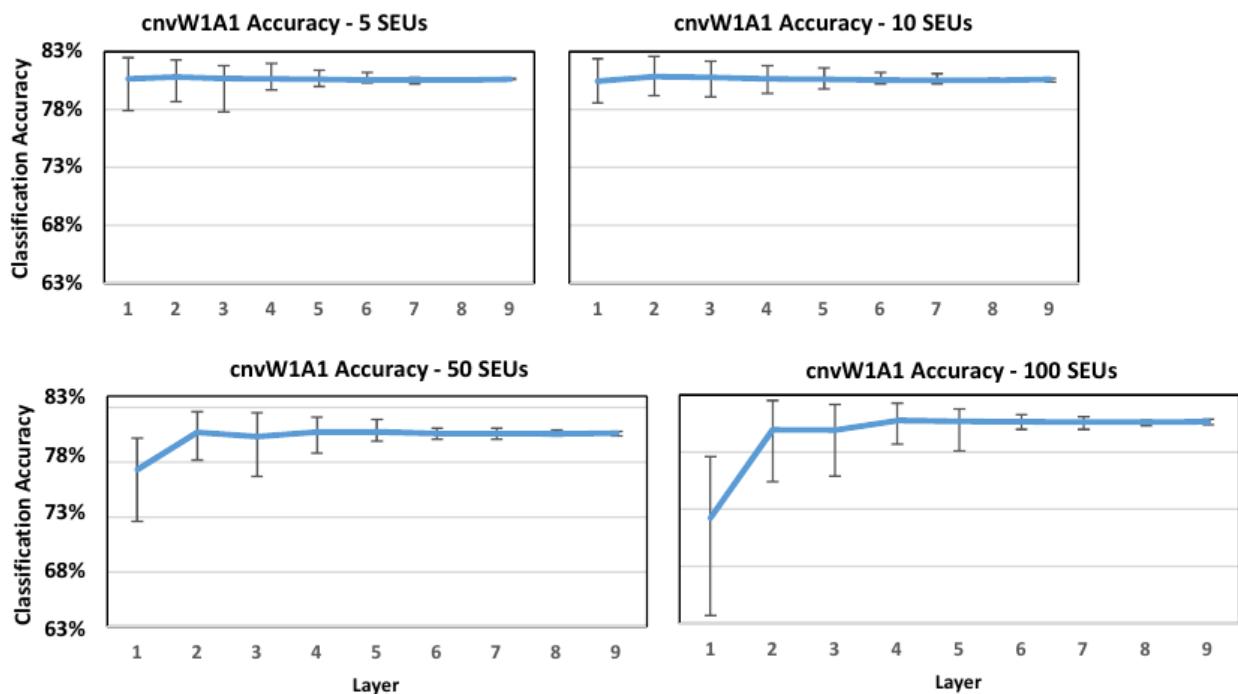

| 9.3.1. Klassifikation . . . . .                                             | 108        |

| 9.3.2. Verstärkung durch Parallelisierung . . . . .                         | 109        |

| 9.4. Maßnahmen . . . . .                                                    | 109        |

| 9.4.1. TMR: Triple Modular Redundancy . . . . .                             | 109        |

| 9.4.2. AdAM: Adaptive Fault-Tolerant Approximate Multiplier . . . . .       | 110        |

| 9.4.3. Symptom-based Error Detectors (SED) . . . . .                        | 112        |

| 9.4.4. Selective Latch Hardening (SLH) . . . . .                            | 113        |

| 9.4.5. FORTUNE: Fault TOleRance TechniqUe . . . . .                         | 114        |

| 9.5. Evaluationsmethoden zur Fehlertoleranz von neuronalen Netzen . . . . . | 116        |

| 9.5.1. Fault Injection . . . . .                                            | 116        |

| 9.5.2. Analytische Methoden . . . . .                                       | 128        |

| 9.5.3. Hybride Methoden . . . . .                                           | 130        |

| 9.6. Zusammenfassung . . . . .                                              | 130        |

| <b>10. Zusammenfassung der Ergebnisse</b>                                   | <b>131</b> |

| <b>11. Ausblick</b>                                                         | <b>135</b> |

| <b>Abbildungsverzeichnis</b>                                                | <b>138</b> |

| <b>Tabellenverzeichnis</b>                                                  | <b>140</b> |

| <b>Abkürzungsverzeichnis</b>                                                | <b>142</b> |

| <b>Literaturverzeichnis</b>                                                 | <b>145</b> |

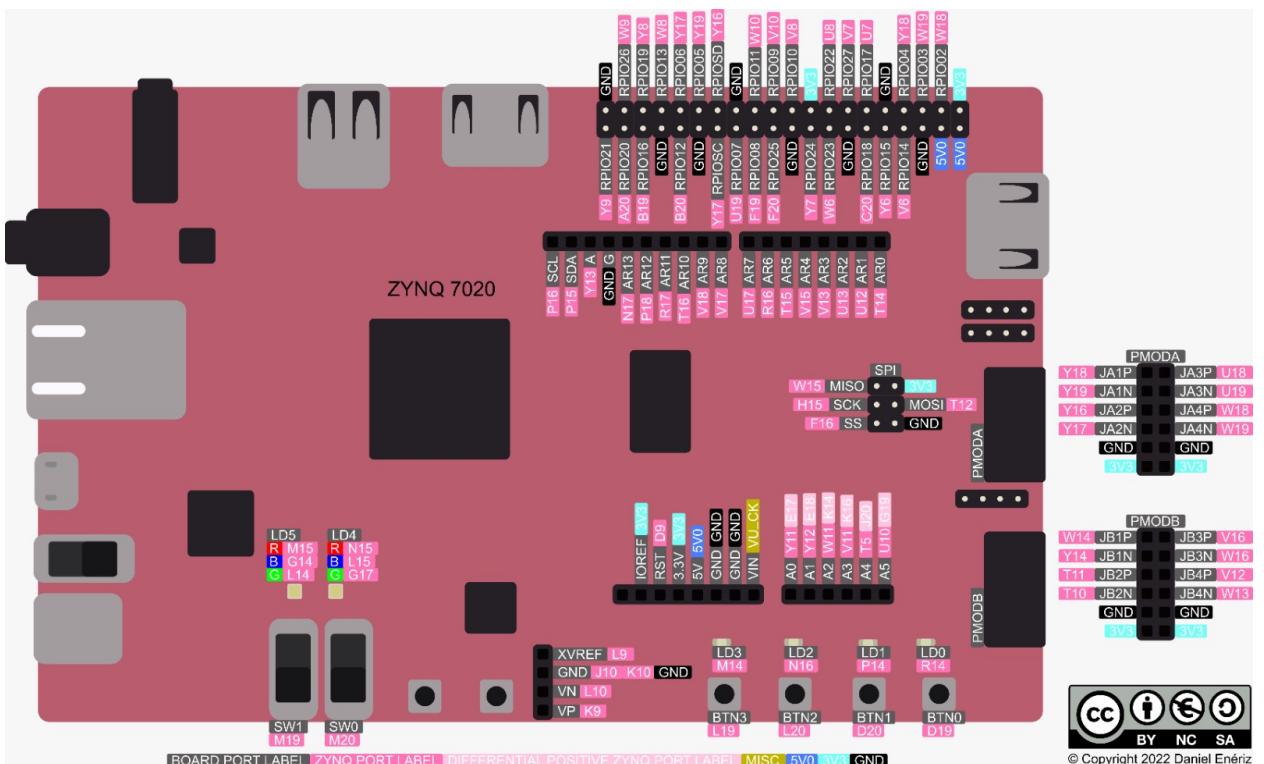

| <b>A. Pinbelegung auf dem PYNQ-Z2-Board</b>                                 | <b>153</b> |

| <b>B. Anleitung zur Nutzung der Fahrsteuerung</b>                           | <b>154</b> |

| B.1. Voraussetzungen . . . . .                                              | 154        |

| B.2. Überblick über die Architektur . . . . .                               | 154        |

| B.3. Aufbau des Fahrzeugs . . . . .                                         | 154        |

| B.4. Verbindung mit dem Board . . . . .                                     | 154        |

| B.5. Einrichtung des Board . . . . .                                        | 155        |

---

|                                                                        |            |

|------------------------------------------------------------------------|------------|

| B.6. Verbinden mit dem WLAN des Boards . . . . .                       | 155        |

| B.7. Nutzung des Front-Ends . . . . .                                  | 155        |

| <b>C. Einrichten eines WLAN-AcessPoints (AP)</b>                       | <b>156</b> |

| C.1. Einrichtung . . . . .                                             | 156        |

| <b>D. Einrichtung des Python-Servers als Service</b>                   | <b>159</b> |

| D.1. Manuelles Starten des Servers in der richtigen Umgebung . . . . . | 159        |

| D.2. Paketanforderungen an die Umgebung . . . . .                      | 160        |

| <b>E. Installationsanleitung: FINN und Xilinx Toolchain unter WSL2</b> | <b>161</b> |

| <b>F. Training des Modells für die Personenerkennung</b>               | <b>164</b> |

| F.1. Installation von Nvidia CUDA und Integration mit torch . . . . .  | 164        |

| <b>G. Überblick über die Git-Repositories</b>                          | <b>165</b> |

| G.1. Öffentliche Repositories . . . . .                                | 165        |

| G.2. Hochschulinterne Repositories . . . . .                           | 165        |

# 1. Einleitung

*geschrieben von Jan Bredereke*

Dies ist der Projektbericht zum Mini-Projekt in der Lehrveranstaltung „Eingebettete Systeme in der Praxis“ (ESYSP) an der Hochschule Bremen im Sommersemester 2025. Dieses Kapitel führt zunächst in den Kontext ein und präsentiert dann die Forschungsfrage. Anschließend stellt es die Beispielanwendung und einschlägige vorhergehende Arbeiten an der Hochschule Bremen vor. Das Kapitel schließt mit einem Überblick über die in der aktuellen Runde des Projekts behandelten Teilthemen.

## 1.1. Kontext

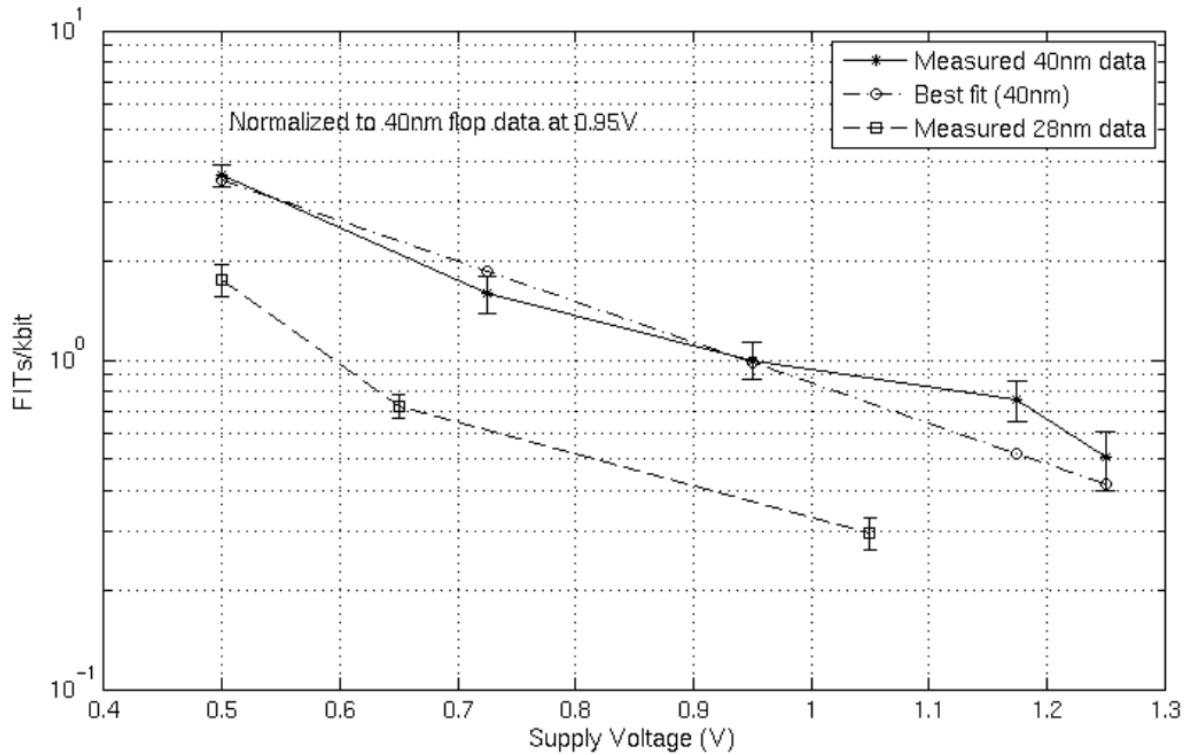

Die Motivation für das Projekt entstammt der Raumfahrt. Auf Bordrechnern ist besonders wenig Rechenleistung verfügbar, und eine Verbindung zu einer Bodenstation ist meist nur zeitweise gegeben. Aufgrund der hohen Belastung durch Weltraumstrahlung würden übliche heutige Prozessoren sehr schnell ausfallen. Daher verwendet man Spezialrechner, deren Chips Strukturbreiten von mindestens 65 nm aufweisen. Diese Spezialrechner sind robust genug, aber entsprechend weniger leistungsfähig als solche, die mit aktuellen 5 nm hergestellt sind.

Aufgrund der äußerst geringen Stückzahlen dieser Art von Rechnern werden sie oft nicht mit speziell entwickelten Chips (ASICs), sondern mit programmierbarer Standard-Hardware (FPGAs) realisiert. Strahlungsfeste Versionen bestimmter FPGAs mit entsprechend großer Strukturbreite sind hierfür verfügbar.

Zunehmend besteht Bedarf an mehr Onboard-Rechenleistung, zum Beispiel für Bildverarbeitung an Bord, etwa für autonome Rover auf anderen Himmelskörpern oder für Schwärme von Kleinsatelliten mit jeweils nur wenig Bandbreite zu einer Bodenstation.

Insbesondere möchte man gerne neuronale Netze nutzen, die üblicherweise in Rechenzentren mit leistungstarker und stromhungriger Spezialhardware eingesetzt werden. Sie können allerdings nicht einfach am Rande der Cloud („Edge“), d.h. nahe bei den Sensoren und Aktoren, oder gar autonom von Daten- und Stromversorgungsverbindungen, auf einem Mikrocontroller eingesetzt werden, denn die CPU eines Mikrocontrollers ist dafür zu rechenschwach.

Mehr Leistung, sowohl absolut als auch pro Stromverbrauch, verspricht der Einsatz eines feldprogrammierbaren Gate-Arrays (FPGA). Grundsätzlich ist ein FPGA für die hochparallele Struktur eines neuronalen Netzes sehr gut geeignet. In der Praxis ergeben sich aber viele Optimierungsaufgaben, die erst gelöst werden müssen, bevor das FPGA diesen Vorteil voll ausspielen kann.

## 1.2. Forschungsfrage

Unsere Forschungsfrage ist, wie man neuronale Netze auf FPGAs am besten nutzen kann, die so leistungsbeschränkt wie strahlungsfeste FPGAs sind. Etwas allgemeiner stellt sich diese Frage entsprechend für neuronale Netze auf FPGAs für Edge-Computing.

## 1.3. Die Beispielanwendung

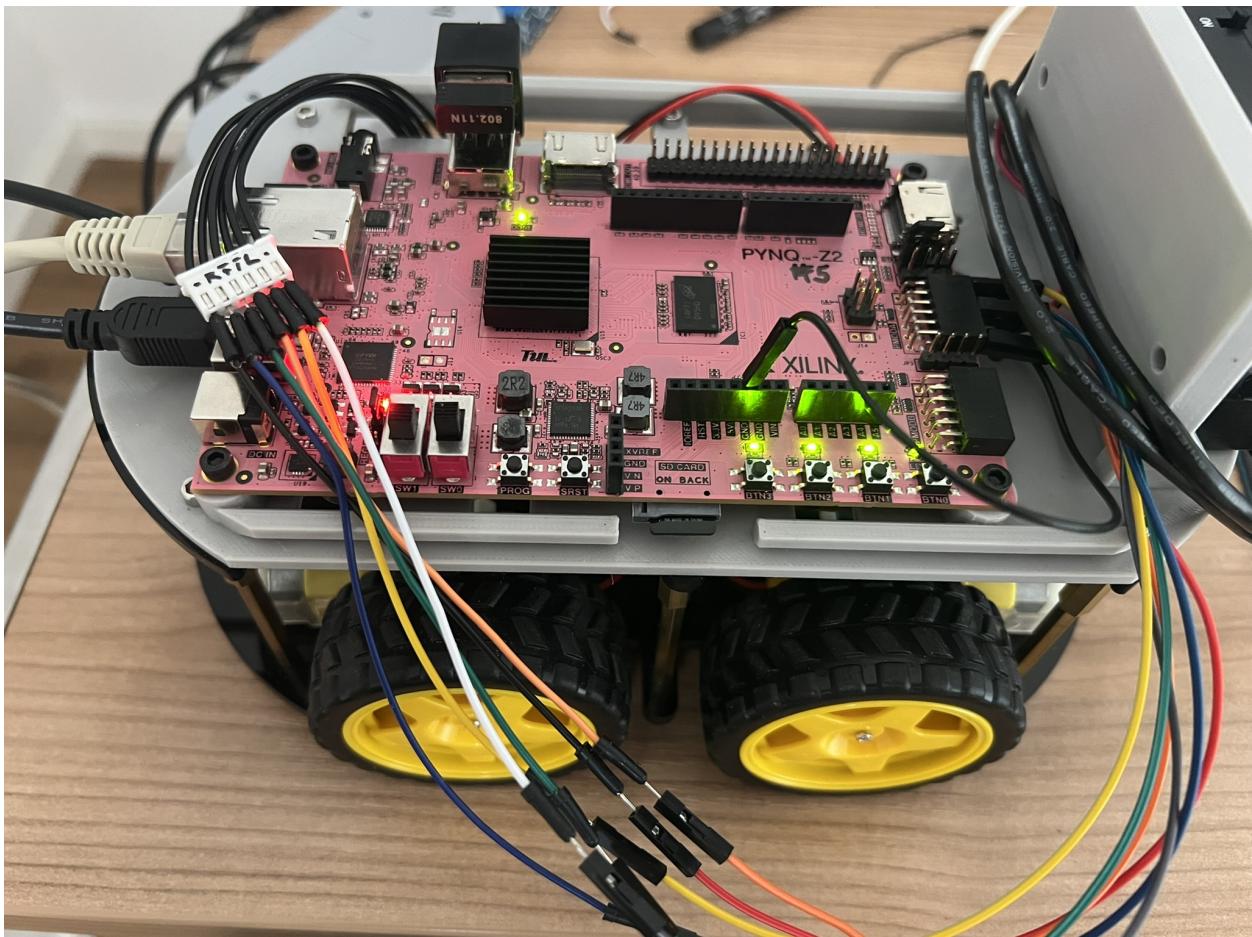

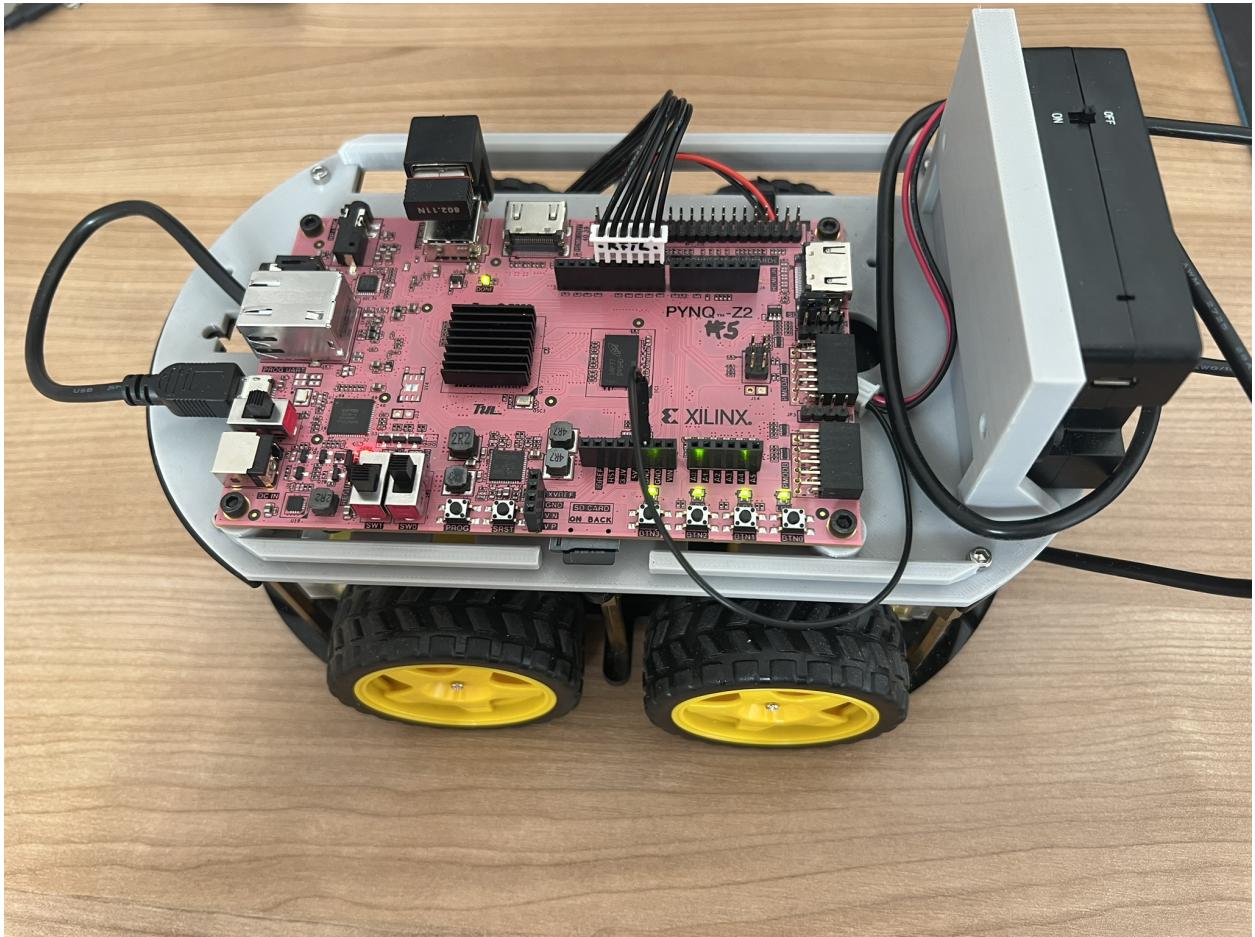

Ein autonomes Modellauto als konkretes Vehikel (siehe Abb. 1.1) dient uns als Stellvertreter für ein autonomes Raumfahrzeug. Es ist mit einer Kamera, einem Mikrofon und einem SoC Zync-7020 ausgerüstet. Das SoC enthält außer einer Arm-CPU auch ein FPGA Artix-7, dessen Leistungsfähigkeit recht gut einem weltraumtauglichen FPGA entspricht. Das SoC ist auf einem PYNQ-Z2 Board verbaut.

Abbildung 1.1.: Das Fahrzeug der Lehrveranstaltung ESYSP im SoSe 2025.

Foto: Frederic Goretzky

## 1.4. Vorhergehende Arbeiten an der Hochschule Bremen

### 1.4.1. Bilderkennung

Die Lehrveranstaltung „Projekt: SoC-NN – FPGAs für neuronale Netze: Edge Computing auf autonomen Vehikeln“ im Wintersemester 2021/22 sowie einige Lehrveranstaltungen davor [ACB+22; ACB+21; Mül21; MKB+21; HSB+20] realisierten eine Bilderkennung: Das Fahrzeug soll autonom und in Echtzeit eine Person in ihrem Blickfeld erkennen, dieser Person folgen, wenn sie sich bewegt, und Fahrkommandos durch einfache Gesten gehorchen.

Der Konferenzbeitrag [Bre23] fasst die Ergebnisse dieser Arbeiten zusammen. Das Erkennen und Verfolgen einer Person durch das Fahrzeug wurde erfolgreich realisiert. Die Gestenerkennung wurde ebenfalls realisiert, konnte aus Zeitgründen allerdings nicht mehr in das Fahrzeug integriert werden. Das Zerlegen eines Bildes eines Videostroms in einzelne Kacheln, die klein genug für eine Analyse durch das neuronale Netz auf einem FPGA sind, wurde von Müller in seiner Abschlussarbeit auf einem FPGA [Mül21] effizient und flexibel implementiert; die Integration in das Gesamtsystem steht jedoch noch aus.

### 1.4.2. Sprachkommandoerkennung

Die Lehrveranstaltung „Embedded Systems“ im Wintersemester 2021/22 [HHB+22] begann im Rahmen des zugehörigen Mini-Projekts, auf dem selben Vehikel eine Fahrsteuerung durch Sprachkommandos statt durch Gesten zu realisieren, ebenfalls autonom und in Echtzeit. Damit stiegen wir neu in den Bereich der akustischen Signale ein. In diesem Gebiet gibt es weniger fertige Lösungen für neuronale Netze als für die Bilderkennung. Dieses Mini-Projekt erstellte ein Konzept, und es produzierte Trainingsdaten, es kam aber auf Grund der beschränkten Zeit noch nicht weiter.

Die Lehrveranstaltung „Embedded Systems“ im Wintersemester 2022/23 [BBJ+23] begann mit der Umsetzung. Hardware-Grundlage war weiterhin das FPGA-Board PYNQ-Z1. Die Systemarchitektur wurde, aufbauend auf dem obigen Vorgängerprojekt, detailliert ausgearbeitet. Ein Teil der Audiodatenverarbeitung wurde auf dem FPGA realisiert. Die Qualität von Trainingsdaten, die aus dem Vorgängerprojekt übernommen wurden, wurde verbessert, und es wurde ein systematisches Problem beim Aufnehmen von Trainingsdaten identifiziert und behoben. Es wurde die Möglichkeit geschaffen, einfacher verschiedene Strukturen für das neuronale Netz zu erstellen, um damit zu experimentieren. Es wurden bereits viele Schritte für die Implementierung des neuronalen Netzes auf dem FPGA ausgearbeitet; die Integration mit der Audiodatenverarbeitung konnte allerdings nicht mehr realisiert werden. Erste Zeitmessungen zeigten, dass der Einsatz eines quantisierten neuronalen Netzes die Verwendung von Fließkommazahlen bei der Inferenz überflüssig macht, welche ohne eine leistungshungrige Hardware nicht verfügbar sind. Zur Erkennungsrate für Sprachkommandos auf dem FPGA lagen bei Projektende noch keine aussagekräftigen Daten vor.

Die Lehrveranstaltung „Embedded Systems“ im Wintersemester 2024/25 [ABB+25] setzte die Arbeit fort. Es wurden die nötigen Verarbeitungsschritte an neue Audio-Hardware angepasst sowie detaillierter identifiziert und festgelegt. Aus einem aufgetretenen Schnittstellenproblem heraus ergab sich eine neue Einsicht zu einer Systemarchitektur für eine effiziente Verarbeitung auf einem FPGA.

## 1.5. Behandelte Teilthemen in der aktuellen Runde des Projekts

In der aktuellen Runde des Projekts werden die oben beschriebenen angefangenen Arbeiten weiter vorangetrieben. Dabei werden sowohl die Bild- als auch die Audioverarbeitung unter den Randbedingungen der schwachen Hardware verbessert, um das Verständnis für die Optimierungsmöglichkeiten zu vertiefen. Unterstützend wird die verwendete Plattform ebenfalls verbessert. Schließlich wird als neues Teilthema ein Verständnis für die Eigenschaften von neuronalen Netzen auf Hardware unter Weltraumstrahlung aufgebaut.

Im einzelnen werden in diesem Bericht die folgenden Teilthemen behandelt:

- Es wird ein Überblick über die geplante Gesamt-Systemarchitektur erarbeitet, um sowohl die Komponenten als auch die Schnittstellen zwischen ihnen zu definieren.

- Bei der Personenerkennung wird analysiert, warum die bisherigen Ergebnisse des Testskripts nicht zum Ergebnis des End-to-End Tests passen. Zusätzlich wird das Trainings- und Testskript verbessert, sowie ein objektiv beurteilbarer Test für die Personenerkennung erstellt.

- Die Toolchain für die hardwarebeschleunigte Gestenerkennung auf dem PYNQ-Z2 Board wird reevaluiert.

- Beim neuronale Netz für die Spracherkennung werden mögliche systematische Fehler analysiert und ausgeschlossen bzw. behoben.

- Die Fahrsteuerung wird analysiert, modularisiert und genauer gemacht.

- Die Elektronik und Mechanik der Fahrzeuge wird verbessert.

- Es wird Forschungsliteratur recherchiert, die die Auswirkungen von Rechenfehlern in einem neuronalen Netz abschätzt. Darüber hinaus werden sowohl Härtungsmaßnahmen zum Schutz vor Rechenfehlern als auch systematische Evaluationsmethoden zur Bewertung der Fehlertoleranz behandelt. Dies ist der Einstieg in ein weitergehendes Thema im selben Kontext von FPGAs für Weltraumanwendungen.

# 2. Überblick über die Systemarchitektur

geschrieben von *Enrico Ramm und Luca Bianchi*

Ziel dieses Kapitels ist es, einen einheitlichen und sinnvollen Gesamtüberblick über die Systemarchitektur des Projekts zu geben. Gerade in einem technisch breit gefächerten Projekt wie diesem ist eine übergreifende Systembeschreibung essenziell, um die Funktionsweise des Gesamtsystems zu verstehen und die Zusammenarbeit zwischen den beteiligten Gruppen zu koordinieren. Daher wird an zukünftige Gruppen appelliert, dieses Kapitel auch in den Folgeberichten fortzuführen und ggf. um detailliertere Schnittstellendetails zu erweitern.

In den letzten Projekten aus den Wintersemestern 2023/2024 [BJB+23] 2022/2023 [HHB+22] 2021/2022 [MKB+21] lag der Fokus stark auf Funktionen wie die Sprachkommandoerkennung, jedoch sind Aspekte wie die gemeinsame Nutzung bzw. Integration dieser innerhalb des Gesamtsystems nicht näher behandelt worden.

In diesem Kapitel wird zuerst ein Überblick über die bislang erreichten Ergebnisse im Kontext einer definierten Gesamtarchitektur erarbeitet und beschrieben (siehe Abschnitt 2.1).

Anschließend wird im Abschnitt 2.3 das in diesem Projekt geplante Architekturkonzept erläutert, indem die Hauptfunktionen der wichtigsten Teilsysteme zusammengefasst und deren zentrale Schnittstellen definiert werden. Die Komponenten des Projekts werden aus unterschiedlichen Perspektiven beschrieben, sowohl aus logischer Sicht als auch unter datenflussorientierten Gesichtspunkten. Außerdem wird erwähnt, welche Teile der geplanten Architektur bereits vorhanden sind.

## 2.1. Vorherige Ergebnisse

Wie zu Beginn dieses Berichtes erwähnt, baut das vorherige autonome System auf den PYNQ Z1 Board auf. Im Kern des PYNQ Z1 Boards arbeitet ein SoC (System on a chip) vom Modell Zynq-7020, welcher in PS (Processing System) und PL (Programmable Logic) unterteilt werden kann. Zum PS gehören zum einen ein ARM Cortex A9 Prozessor, der via Schnittstellen Zugriff auf den Arbeitsspeicher, Peripherie und I/O, sowie den FPGA (PL) Teil des SoCs besitzt. Der PL ist der FPGA-Teil des SoCs, wodurch dieser sich individuell programmieren lässt, um schnelle Hardware-Logik ausführen zu können.

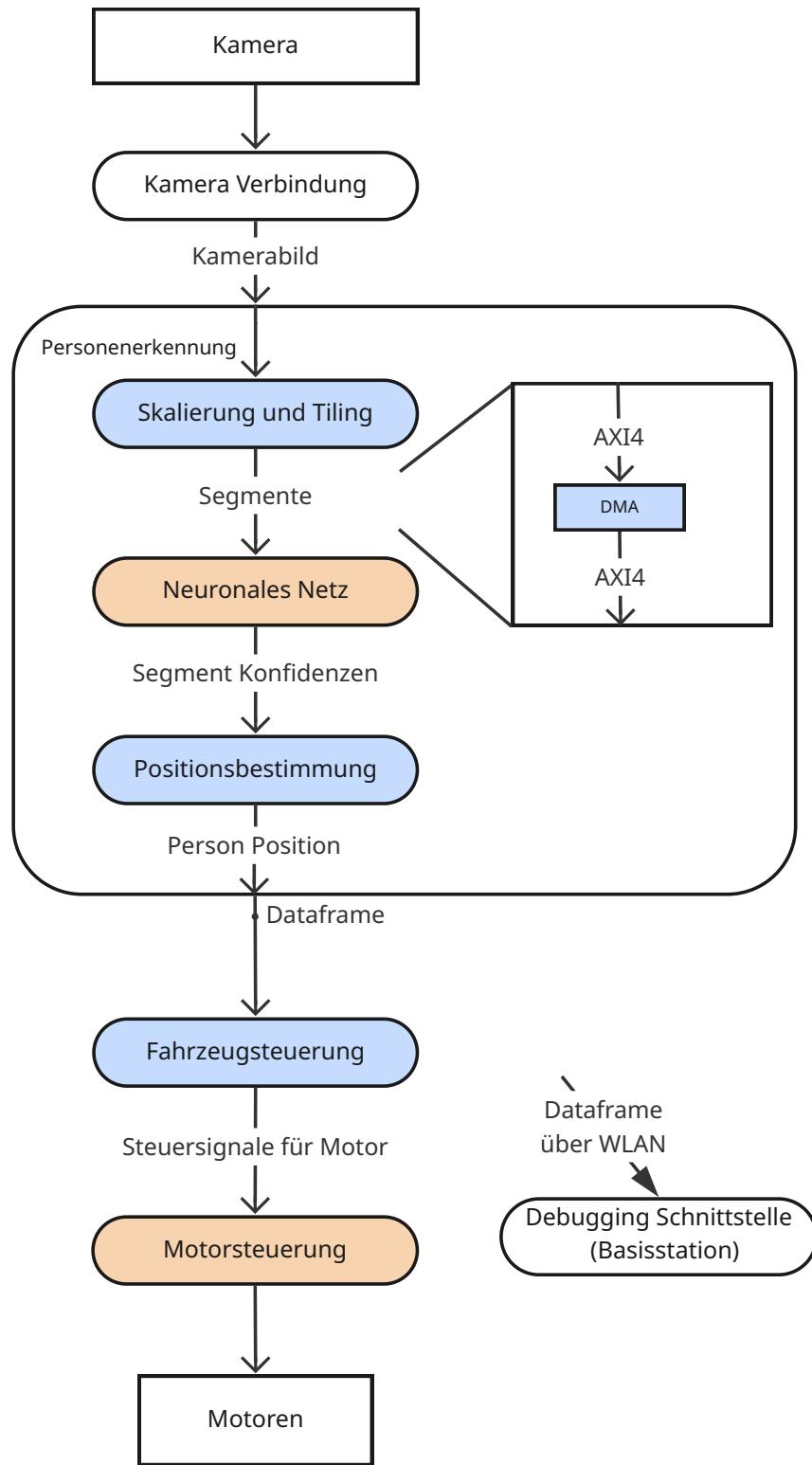

Die Gesamtarchitektur der vorherigen Projekte lässt sich als mehrstufige, eng gekoppelte Signal- und Datenverarbeitungskette beschreiben, die von der Kamera-Ebene bis zur Motoransteuerung reicht (vgl. Abbildung 2.1). Um die Hardware-Beschleunigung auf dem Board zu nutzen, werden unterschiedliche Module entweder auf dem PS (hier blau markiert) oder dem PL (hier orange markiert) ausgeführt.

Im Folgenden werden die wesentlichen Verarbeitungsschritte erläutert.

**Kamera-Akquisition und Übertragung** Das Fahrzeug führt eine USB-Kamera, deren Rohdaten in der Kamera-Verbindung zunächst mittels Video4Linux-Treibern auf dem ARM-Teil des Zynq-7020 SoC empfangen werden. Das resultierende RGB-Bild dient als einziger Sensoreingang für die Folgeketten.

**Personspezifische Bildvorverarbeitung** Innerhalb des Personenerkennungs-Moduls wird das Kamerabild zuerst skaliert und in überlappende Tiles zerlegt. Das Sliding-Window-Verfahren reduziert dabei den Eingaberaum so weit, dass jedes Tile einer Person potenziell objektfüllend entspricht, ohne die hohe globale Auflösung beibehalten zu müssen. Auf dem PYNQ-Z1 führt ein dedizierter TilingController diese Aufgabe aus.

**Positionsbestimmung** Die Konfidenz-Map aller Tiles wird softwareseitig aggregiert. Ein Maximum-Suche-Algorithmus bestimmt das Tile-Zentrum mit der höchsten Wahrscheinlichkeit und gibt dessen Pixelkoordinaten als Person Position aus. Diese Verdichtung reduziert den Datenstrom auf wenige Bytes pro Bild und übergibt ein abstraktes Weltmodell an die nachfolgende Regelungsschicht. Im Abschnitt 3 wird genauer auf die Personenerkennung eingegangen.

**Fahrzeugregelung und Motorsteuerung** Die Fahrzeugsteuerung interpretiert die Position relativ zum Bildmittelpunkt als Regelgröße. Ein diskreter PID-Regler erzeugt Soll-Geschwindigkeiten für Lenk- und Fahrmotor, um die Person mittig und in konstanter Distanz zu halten. Alle Reglerparameter sind im Python-Teil des SoC adaptiv konfigurierbar und wurden empirisch auf das Chassis abgestimmt.

Das Motorsteuerungs-Modul setzt die Reglerausgaben in PWM-Signale für Heck- und Lenkservomotor um. Hierzu nutzt es ein leichtgewichtiges AXI-Lite-Interface, sodass die Steuerzyklen deterministisch innerhalb der Video-Frame-Zeit erfolgen können.

**Telemetrie- und Debug-Pfad** Parallel zum Echtzeitpfad überträgt das System jedes verarbeitete Frame-Resultat als DataFrame via WLAN an eine Basestation. Die Debug-Schnittstelle visualisiert Konfidenzkarten, Tiles und Reglergrößen in Jupyter-Notebooks, wodurch Parameter-Tuning und Fehlersuche ohne zusätzliche Logik auf dem Fahrzeug erfolgen können.

Abbildung 2.1.: Vorherige Architektur (Hauptmodule und Datenpfad)

## 2.2. Datenaustausch zwischen PS und PL

Aufgrund der Aufteilung der funktionalen Module zwischen PS und PL, stellt sich die Übertragung von Daten von der Software zur programmierten Hardware als sehr wichtig dar. Um den Kommunikationsweg genauer zu verstehen, wird der Datentransfer zwischen PS und PL (genauer

zwischen CPU und neuronalen Netz) in diesem Abschnitt beschrieben. Zudem ist es anzumerken, dass diese Themen bereits ausführlicher in den vorherigen Projekt-Berichten [\[HSB+20\]](#) und [\[ACB+21\]](#) erläutert wurden, weshalb hier Nötigste zusammengefasst wird.

### 2.2.1. AXI (Advanced Extensible Interface)

Das Advanced Extensible Interface oder kurz AXI, ist ein Protokoll-Standard, welcher Teil der von ARM gepflegten Protokoll-Familie AMBA (Advanced Microcontroller Bus Architecture) ist. Hierbei besitzt AXI4 die Untervarianten AXI4, AXI4-Lite und AXI4-Stream, welche leistungsstark sind und ein breites Spektrum an Datentransfer-Bedürfnissen abdecken (vgl. [\[Arm25\]](#)).

Im Kern des AXI-Protokolls kommunizieren Komponenten als Master (Manager) und Slave (Subordinate) miteinander, wobei der Master mittels Adresse Daten von einem Slave lesen oder an einen Slave senden kann. AXI definiert hierbei nur eine 1 zu 1 Verbindung, weshalb bei gleichzeitiger Kommunikation zwischen mehreren Master- und Slave-Komponenten eine AXI-Interconnect-Komponente die Verbindungen dieser steuert bzw. verwaltet. Eine genauere Beschreibung der AXI-Schnittstellen (AXI-Lite, AXI-Stream) kann im Kapitel 2.10 des Berichts [\[ACB+21\]](#) gefunden werden.

### 2.2.2. Datentransfer zwischen Processing System und neuronalen Netz

Der Datentransfer zwischen CPU und neuronalen Netz wird im Kapitel 9.1.3 des Projektberichts [\[ACB+21\]](#) als Zusammenspiel aus dem DMA (Direct Memory Access)-Speicher, AXI-Lite Bus zur Konfiguration und AXI-Stream zur schnellen Datenübertragung beschrieben. Nachdem die vorverarbeiteten Bild-Tiles von der CPU im externen DDR-RAM abgelegt wurden, werden diese über den DMA-Speicher abgegriffen, um anschließend an den IP-Block des neuronalen Netzes zur Analyse weitergeleitet zu werden. Genauer wird für das Einlesen der Bild-Tiles aus dem RAM ein AXI-Lite Bus verwendet, welcher die bestimmten Speicheradressen und die Größe der zu übertragenen Bilder über Konfigurationsregister setzt. Somit benötigt die CPU nur einige Taktzyklen zum Konfigurieren der Übertragung und überlässt die eigentliche Datenübertragung anschließend dem DMA-Controller, wodurch die CPU während des Transfers entlastet wird.

Nachdem das neuronale Netz die vorverarbeiteten Bilder analysiert hat, werden die aus den Tiles ergebenen Konfidenzergebnisse in einem weiteren DMA-Block (ODMA genannt) direkt geschrieben. Auch hierfür wird die Datenübertragung mittels AXI-Lite konfiguriert, indem die Ziel-Speicheradresse im RAM für den DMA-Block angegeben wird. Ein Statusregister teilt der CPU mit, wann ein Schreibvorgang (also der Durchlauf des NNs) fertig ist, um weiter mit den Konfidenzwerten arbeiten zu können.

### 2.2.3. Verwendete Hilfsquellen zum Verständnis der Projektarchitektur

Wie bereits erwähnt, wurde vor allem in den letzten Projektberichten der Überblick der Gesamtarchitektur als Konsequenz der spezialisierten Betrachtung von Teilespekten eher vernachlässigt. Eine Folge dessen ist, dass viele Informationen im Kontext der Systembeschreibungen über alle Projektberichte verteilt sind. Um diesen entgegenzuwirken, wurde eine Auflistung der wichtigsten Systembeschreibungen aus den vorherigen Projekten zusammengefasst:

Folgende Tabelle listet alle für die Dokumentation der Gesamtbeschreibung verwendeten Hilfsquellen mit ihrer Herkunft und kurzer Beschreibung auf:

| Zweck der Quelle                                                                  | Quelle                      | Anmerkung/Kommentar                                                                                         |

|-----------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------|

| Architektur                                                                       |                             |                                                                                                             |

| Internes Konzept für die interne Verarbeitung der Kamerasignale                   | [ACB+22, S. 25]<br>_____    | Dieser Abschnitt beschreibt die interne Bildverarbeitung mit neuronalen Netzen.                             |

| Überblick der Klassenbeziehungen zwischen Controllerklassen und Fahrzeugsteuerung | [ACB+21, S. 67]<br>_____    | Dieser Abschnitt beschreibt Anpassungen und das bis jetzt aktuell-laufende Design für die Fahrzeugsteuerung |

| Architekturkonzept für Sprachkommandoerkennung                                    | [ABB+25, S. 17]<br>_____    | Dieser Abschnitt beschreibt ein Gesamtsystemkonzept für eine Sprachkommandoerkennung                        |

| Schnittstelle PS und PL                                                           |                             |                                                                                                             |

| AXI-Stream IP-Core & DMA-Loop-Back                                                | [HSB+20, S. 39-41]<br>_____ | Zeigt ein exemplarisches AXI-Stream Projekt                                                                 |

| Datenpfad (AXI-DMA) & Register-Mapping                                            | [ACB+21, S. 67-70]<br>_____ | Gibt Aufschluss über den Datentransfer zwischen Processing System und neuronalem Netz                       |

Tabelle 2.1.: Verwendete Quellen zur Dokumentation der vorherigen Projektarchitektur

## 2.3. Geplante Architektur

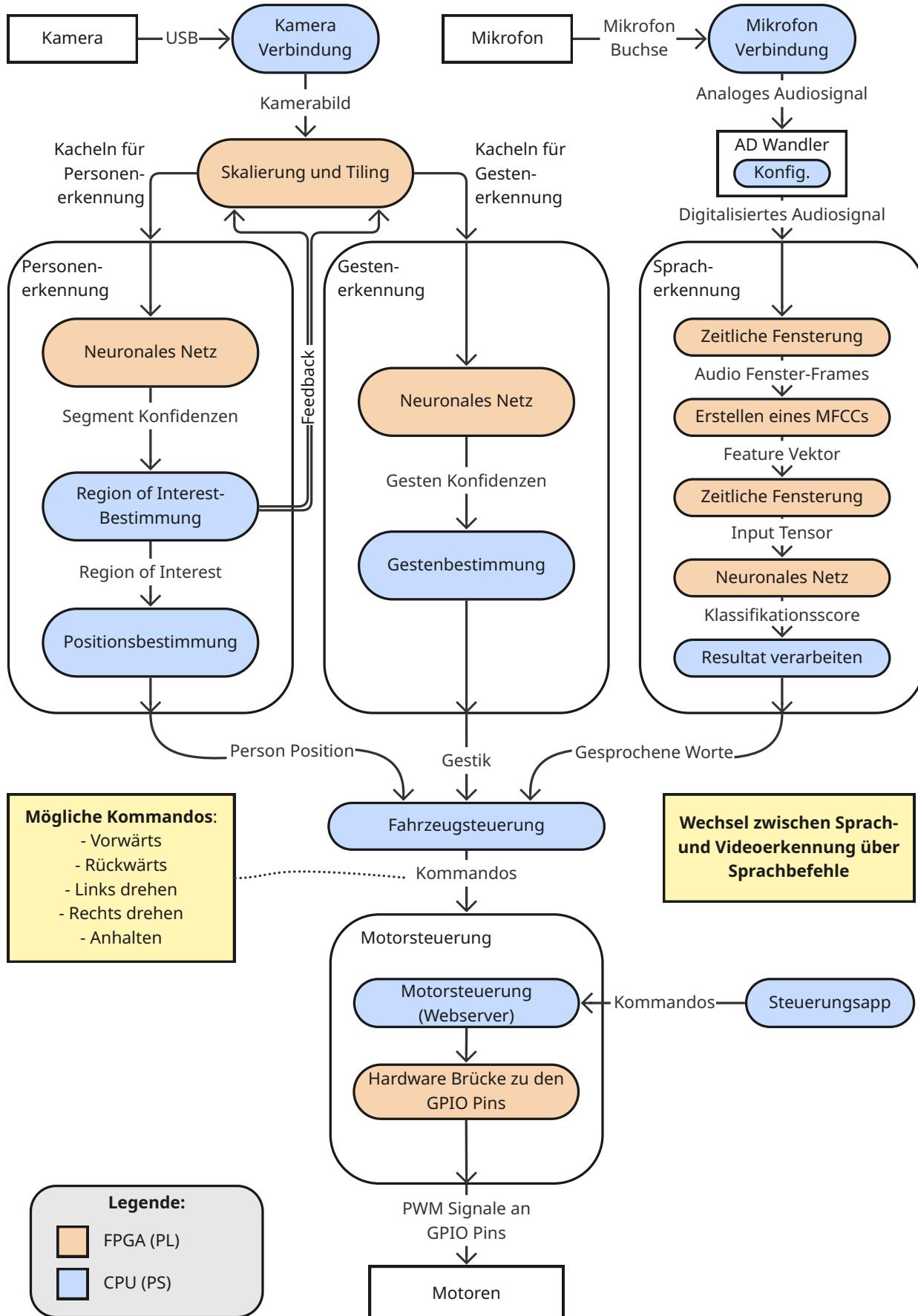

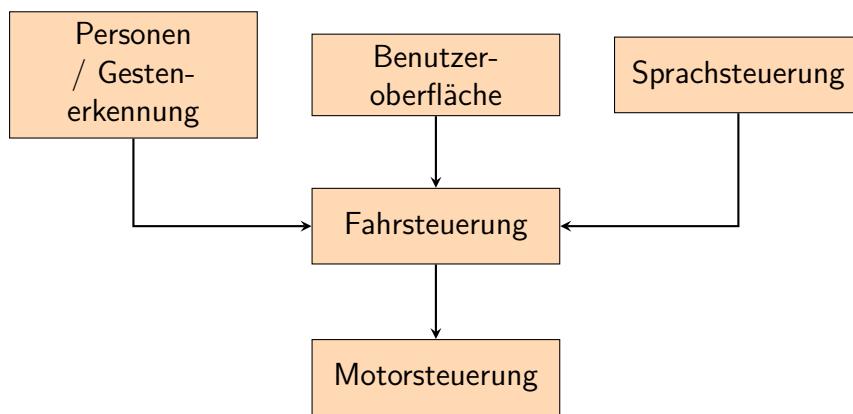

In Abbildung [2.2 auf Seite 12](#) ist die geplante Architektur des Projektes dargestellt. Die Architektur basiert sowohl auf Ansätzen vorheriger Gruppen, als auch neuen Ideen. Dies ist in den folgenden Unterabschnitten entsprechend markiert.

### 2.3.1. Personen- und Gestenerkennung

Die Personen- und Gestenerkennung sind getrennte Module, welche sich jedoch aufgrund ihrer ähnlichen Aufgabe das Untermodul zuständig für die Skalierung und das Tiling teilen. Dieses Untermodul erhält die Bilddaten von einer Kamera, welche über USB und der Kameraanbindung an das System angeschlossen sind. Das Skalierung und Tiling-Untermodul erstellt aus den Bilddaten Kacheln für die Personenerkennung und für die Gestenerkennung.

Die Kacheln für die Personenerkennung werden sequenziell in ein neuronales Netz gegeben. Dieses gibt einen Ausgabevektor mit Segment Konfidenzen für die Eingabe-Tiles aus. Die Segment-Konfidenzen werden genutzt, um mit einem weiteren Untermodul eine Region of Interest (ROI) zu bestimmen. Die ROI wird als Feedback verwendet, um sowohl für die Personen- als auch für die Gestenerkennung die Skalierung und das Tiling zu optimieren. Außerdem wird die ROI verwendet, um die Position der Person im Bild zu bestimmen. Die Position wird an das Modul der Fahrzeugsteuerung weitergegeben.

Die Kacheln für die Gestenerkennung werden in ein weiteres neuronales Netz gegeben. Dieses gibt einen Vektor mit Konfidenzen für einige vordefinierte Gesten aus. Anhand der Konfidenzen werden die verschiedenen Gesten bestimmt. Die jeweilige Geste wird an die Fahrzeugsteuerung weitergegeben.

Rechenintensive Aufgaben, wie die beiden neuronalen Netze und die Skalierung und das Tiling sollen auf dem FPGA (PL) laufen. Alle weiteren Aufgaben, die weniger rechenintensiv sind, sollten aufgrund der einfacheren Implementierung in Software zum Laufen auf der CPU realisiert werden.

*Für das Tiling existiert ein TilingController aus [ACB+21] (siehe Abschnitt 3.3 und Abschnitt 4.2). Auch die Bestimmung der ROI wird in Abschnitt 4.2 beschrieben, jedoch konnte keine abschließende Integration auf dem PYNQ-Z2-Board erreicht werden. Ebenfalls ist die beschriebene Feedback-Schleife für die ROI noch nicht implementiert.*

### 2.3.2. Spracherkennung

Die Spracherkennung erhält das Eingabesignal über ein Mikrofon und die zugehörige Anbindung. Zusätzliches wird das analoge Audiosignal vom AD-Wandler des PYNQ-Z2 digitalisiert. Der AD-Wandler muss vorher in Software konfiguriert werden.

Das digitalisierte Audiosignal wird an das Spracherkennungsmodul gegeben. Der Aufbau des Moduls wurde [ABB+25, S. 17] entnommen. Das kontinuierlich aufgenommene Audiosignal wird in einzelne Fenster aufgeteilt. Diese werden genutzt, um Mel Frequency Cepstral Coefficients (MFCCs) zu erstellen. MFCCs dienen zur kompakten Darstellung eines Frequenzspektrums und werden häufig zur Spracherkennung genutzt [Log+00]. Die MFCCs werden erneut in zeitliche Fenster aufgeteilt, bzw. systematisch zu größeren Fenstern zusammengefügt (z. B., um Fenster zu sammeln, bis ein Bereich von 2 Sekunden abgedeckt ist). Diese Fenster werden anschließend in ein weiteres neuronales Netz gegeben, welches das Audiosignal klassifiziert. Das Ergebnis der Klassifizierung wird zur Verarbeitung weitergegeben, um die gesprochenen Worte daraus zu identifizieren. Die erkannten Worte werden an die Fahrzeugsteuerung weiter gegeben.

*Implementiert wurde in dieser Runde des Projekts eine verbesserte Erkennung einzelner Kommandos, jedoch bisher nur auf dem Laptop (siehe Kapitel 7). Ausstehend ist außerdem die Vervollständigung der beschriebenen Audio-Pipeline.*

### 2.3.3. Fahrzeug- und Motorsteuerung

Die Fahrzeugsteuerung erhält folgende Eingabesignale:

- Von der Personenerkennung die Position der Person im Bild

- Von der Gestenerkennung die erkannte Geste

- Von der Spracherkennung die erkannten gesprochenen Worte

Anhand der Eingabesignale entscheidet die Fahzeugsteuerung welches Kommando an die Motorsteuerung gesendet wird. Die Umsetzung soll dabei einfach und intuitiv gestaltet sein. Z. B. wenn die Personenerkennung die Position der Person im Bild innerhalb eines gewissen Bereiches auf der linken Seite des Bildes angibt, soll sich das Fahrzeug nach links drehen. Oder wenn der Befehl „Vorwärts“ gesprochen wird, soll das Fahrzeug nach vorne fahren. Der Wechsel zwischen Personen-, Gesten- und Spracherkennung soll über Sprachbefehle geschehen.

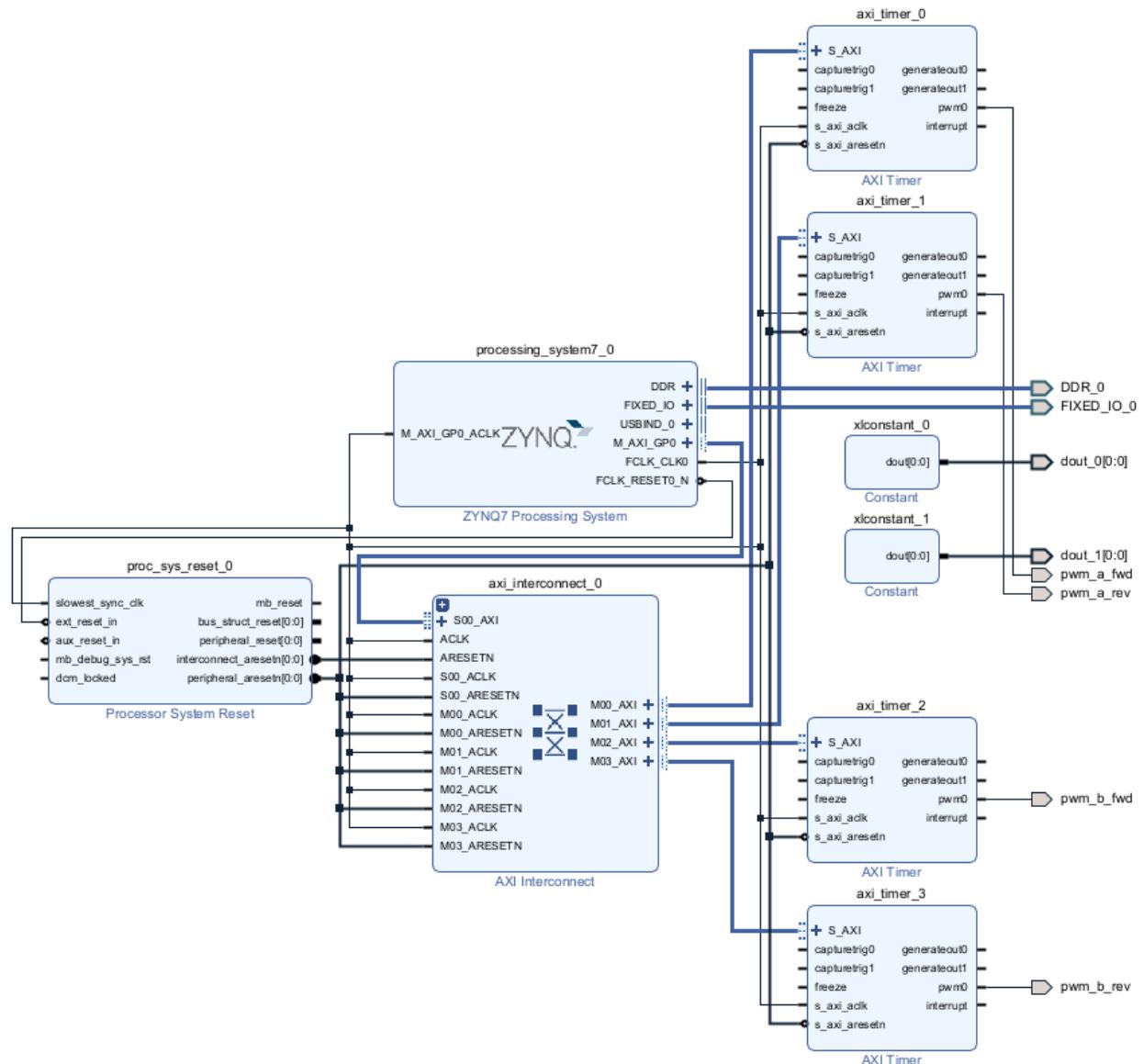

Die von der Fahrzeugsteuerung bestimmten Befehle werden von der Motorsteuerung durch die Ausgabe von einer entsprechenden Spannung an den Motor-Pins umgesetzt. Die Motorsteuerung läuft in Software. Da jedoch die GPIO Pins nicht von der Software aus angesteuert werden können, muss auf dem FPGA eine Hardwarebrücke zu den Pins aufgesetzt werden.

Die Motorsteuerung enthält ebenfalls einen Webserver. Über eine Steuerungsapp können so direkt Befehle an die Motorsteuerung gegeben werden. Dies dient zum Testen und Debuggen der Motorsteuerung, solange die Personen-, Gesten- und Spracherkennungsmodule noch nicht zuverlässig funktionieren.

*In dieser Runde des Projekts wurde die alte Motorsteuerung (geschrieben in C++) verworfen und vollständig neu in Python implementiert (siehe [Unterabschnitt 5.3.6](#)). Ebenfalls wurde eine Hardwarebrücke zu den Pins eingerichtet (siehe [Unterabschnitt 5.1.2](#)) und der Webserver samt Steuerungsapp implementiert (siehe [Kapitel 5](#)). Noch nicht implementiert ist die Umsetzung der Eingabesignale der Personen-, Gesten- und Spracherkennung in Befehle für die Motorsteuerung, sowie Sprachbefehle zum Wechsel den drei Eingabemethoden.*

Abbildung 2.2.: Geplante Architektur

# 3. Personenerkennung

geschrieben von Keno Albers, Jonas Broda, Julius Böttger, Jannik Hennicke, Nils van Rijsinge

## 3.1. Behandelte Themen

Die ursprüngliche Aufgabenstellung lautete: „Analyse, warum der Ende-zu-Ende-Systemtest nicht ganz so gute Erkennungsergebnisse lieferte wie das Validierungsskript“. Während der Recherche im Bericht aus dem Wintersemester 2021/22 [ACB+22] stellte sich jedoch heraus, dass der Systemtest bessere Ergebnisse liefert und das „Validierungsskript“ fehlerhaft ist. Zudem ist der Systemtest als nicht aussagekräftig und reproduzierbar zu bewerten und auch das Trainingsskript bedarf noch Verbesserungen. Daraus ergaben sich drei Aufgabenstellungen bzw. -bereiche. Auf der einen Seite sollen sowohl der Trainingsprozess als auch das „Validierungsskript“ verbessert werden (Abschnitt 3.4 und Abschnitt 3.5). Auf der anderen Seite ist das Ziel, eine neue Testmethode für den Ende-zu-Ende-Systemtest zu entwickeln (Abschnitt 3.6). Diese soll einen zuverlässigen, aussagekräftigen und nachvollziehbaren Wert liefern. Bestenfalls liefert die Überprüfung der Genauigkeit des Modells via „Validierungsskript“ dann einen deutlich besseren Wert und der Unterschied der Resultate der beiden Testverfahren ist nicht mehr so groß.

## 3.2. Grundlagen

### 3.2.1. Overfitting

Zum Trainieren von neuronalen Netzen, die in der Lage sind, auf neue, ungesehene Daten generalisiert zu reagieren, ist eine Modellbewertung ein entscheidender Schritt [WBM23]. Ein bekanntes Problem hierbei ist Overfitting, bei dem ein Model nicht gut von bekannten Daten auf neue Daten generalisieren kann. [Yin19]. Einfacher ausgedrückt beschreibt Overfitting den Vorgang, bei welchem ein neuronales Netz, oder ein KI-Lerner im Allgemeinen, die Daten so sehr annähert, dass dieser diese im Grunde „auswendig“ lernt, aber sein Gelerntes nicht auf unbekannte Daten anwenden kann. Dies kann auch mit einer begrenzten Anzahl von Daten und bereits nach wenigen Trainingsphasen auftreten [CT10].

Für Overfitting kann es unterschiedliche Gründe geben. Diese können in drei Kategorien unterteilt werden. Zum einen das Auswendiglernen von Rauschen in den Daten, ohne das dahinterliegende Konzept zu verstehen. Dies passiert oftmals, wenn es zu wenig Daten oder Daten gibt, die die wichtigen Informationen nicht gut abbilden. Eine weitere Ursache liegt in der Balance zwischen „accuracy“ (Genauigkeit) und „consistency“ (Konsistenz). Wenn die Genauigkeit erhöht werden soll, kann die Komplexität bzw. die Anzahl der Eingänge erhöht werden, dies verringert jedoch die Konsistenz. Somit wie gut das Modell auf andere Daten angewendet werden kann. Die dritte Kategorie beschreibt das Problem bei der Auswahl von guten Modellen. Diese werden basierend auf bestimmten „scores“ und Bewertungsfunktionen ausgewählt. Da jedoch immer das Modell

mit dem besten score gewählt wird, wird ein Modell, welches nur garantiert gut an die gegebenen Daten passt, ausgewählt und nicht garantiert gut generalisiert [Yin19, S. 1-2].

Ein einfaches und bekanntes Verfahren, um Overfitting zu vermeiden ist „Early-Stopping“. Wenn der Accuracy-Score auf Trainingsdaten immer besser wird, wird das Modell aufgrund von Noise-Lernen ab einem gewissen Zeitpunkt schlechter. Zur Überprüfung wird ein Validierungs-Score verwendet, wenn dieser sich nicht verbessert oder sogar schlechter wird, dann ist dies ein direkter Indikator dafür, dass der Lerner gerade auf dem Weg zum Overfitting ist. Das Training sollte abgebrochen bzw. frühzeitig gestoppt werden [Yin19].

### 3.2.2. Stratified Sampling

Beim zufälligen Aufteilen des Datensatzes für Training und Validation gibt es ein Problem. Es kann passieren, dass durch das zufällige Aufsplitten des Datensatzes eine Klasse in Training- oder Validate-Subdatensatz über- beziehungsweise unterrepräsentiert ist. Dies hat zur Folge, dass die berechneten Scores aus Unterabschnitt 3.2.1 nicht mehr aussagekräftig sind, da diese nach unten oder oben verschoben sein können.

Dieses Problem wird mit der Methode des Stratified Sampling gelöst. Die Idee kommt aus der Statistik in der Wirtschafts- und Sozial-Forschung und wurde im KI-Kontext wiederverwendet. Hier wird die "[...] Grundgesamtheit in disjunkte Klassen (Schichten) [aufgeteilt]" [Mos12, S. 4]. Dabei sollen die diese Schichten so gewählt werden, dass sich die Schichten in Bezug auf die Klassen gleich verhalten, also die Verhältnisse erhalten bleiben. Dazu werden  $n$  Schichten gebildet, in welchen dann zufällige Datensätze verschiedener Klassen proportional zu ihrem Vorkommen ausgewählt und dieser Schicht zugeordnet werden. So erhält man  $n$  Schichten in welchen die Klassenverhältnisse annähernd gleich sind.

### 3.2.3. Trainieren von neuronalen Netzen und Modellbewertung

Um die Genauigkeit eines Modells zu bestimmen, werden für verlässliche Aussagen nicht die gleichen Daten, wie beim Training verwendet. Diese könnten aufgrund von Overfitting nicht die tatsächliche Güte des Modells, sondern nur die Anpassung an die Daten beschreiben. Aus diesem Grund werden die Daten aufgeteilt in einen Trainings- und einen Testdatensatz. Zusätzlich können die Trainingsdaten erneut aufgeteilt werden in einen Training- und einen Validierungsdatensatz. [WBM23]

Der Trainingsdatensatz wird dazu verwendet das Netz zu trainieren und die Gewichte so anzupassen, dass sie den Trainingsdatensatz gut annähern. Der Validierungsdatensatz oder auch Cross-Validierungsdatensatz wird noch im Trainingsprozess verwendet, um das Modell optimal zu trainieren. Dieser Datensatz kann mit Cross-Validierung genutzt werden, um verschiedene Algorithmen zu vergleichen und den besten auszuwählen. Auch können die besten Hyperparameter eines Algorithmus ermittelt werden oder ein Overfitting beim Trainieren von neuronalen Netzen festgestellt werden.

Das Testskript wird nach Abschluss des Trainings verwendet, um die Güte des Netzes mit Daten, die es noch nie vorher gesehen hat, zu bestimmen. Damit wird geprüft, ob das Netz wirklich die Eigenschaft der gelernten Klassifikation abbilden kann. [WBM23; LLC22, S. 115ff.]

Die bisher verwendete Metrik für die Güte des Modells (Accuracy) kann z. B. bei stark unausgewogenen Klassen irreführend hoch sein, auch wenn das Modell die Minderheitsklasse schlecht

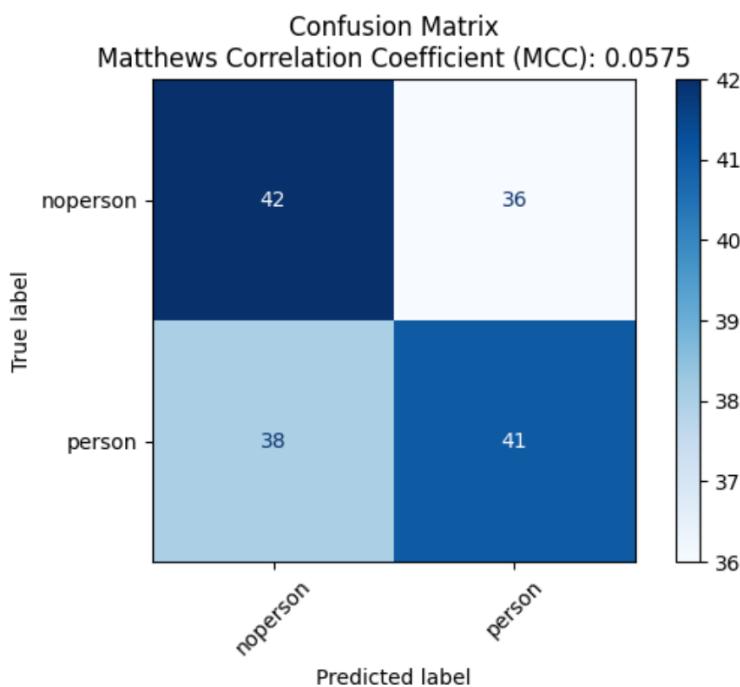

vorhergesagt wurde. Die Accuracy ist insgesamt nicht gut geeignet, wenn nur eine einzelne Metrik als Maß der Güte eines Modells gesucht ist. Matthews Correlation Coefficient (MCC) ist hingegen beliebt für diesen Anwendungsfall. Bei seiner Berechnung werden alle vier Felder der Konfusionsmatrix ( $TP$ ,  $TN$ ,  $FP$ ,  $FN$ ) mit einbezogen:

$$MCC = \frac{(TP \cdot TN) - (FP \cdot FN)}{\sqrt{(TP + FP)(TP + FN)(TN + FP)(TN + FN)}}$$

Der MCC bietet damit einen aussagekräftigeren und vergleichbaren Wert für die Güte verschiedener Modelle. [LLC22, S. 136]

### 3.3. Erkenntnisse aus vorherigen Projektberichten

Im Sommersemester 2021 [ACB+21] wurde sich unter anderem mit der Gestenerkennung beschäftigt. Um die drei Gesten *START*, *STOP* und *NOPOSE* erkennen zu können, wurde ein neuronales Netz mithilfe von Python-Skripten entwickelt (Die Implementation des Trainingsprozesses ist in Abschnitt 3.4 beschrieben). Zum Trainieren und Testen wurde ein Datensatz aus selbst aufgenommenen Bildern erstellt. Als Modellframework wurde Brevitas verwendet, was vor allem durch die Möglichkeit des Exports eines trainierten Modells im ONNX-Format überzeugen konnte. Der Trainingsprozess wurde in einer Cloud-Umgebung ausgeführt, um schneller neuronale Netze trainieren zu können ohne entsprechende eigene Hardware zu benötigen (vgl. [ACB+21, S. 61ff.]). Ein Training auf einer Cloud Graphics Processing Unit (GPU) war dabei jedoch nicht erfolgreich und es wurde auf der CPU trainiert (vgl. [ACB+21, S. 63]).

Zum Ausführen des neuronalen Netzes wurden aus den Bilder Kacheln von  $32 \times 32$  Pixel erzeugt, da das verwendete Modell nicht mit größeren Bildern arbeiten kann. Diese Kacheln werden im *TilingController* auf dem Auto erzeugt. In [ACB+21, S. 73] wird angegeben, dass der *TilingController* aus dem Vorgängerprojekt übernommen wurde. Die genaue Umsetzung des Tilings ist in [MKB+21, S. 23ff.] beschrieben.

Im Wintersemester 2021/22 [ACB+22] wurde an der Personenerkennung und nicht mehr an der Gestenerkennung gearbeitet. Das Ziel war, ein neuronales Netz zu trainieren, dass erkennen kann, ob sich eine Person auf einem gegebenen Bild befindet oder nicht. Die Skripte dafür wurden aus dem vorherigen Semester [ACB+21] übernommen. Der Datensatz basiert auf dem COCO-Datensatz [COC], welcher unter der Creative Commons Attribution 4.0 License [Cre] veröffentlicht worden ist, wurde aber zudem noch manuell gefiltert. So wurden nur Bilder in den Datensatz übernommen, auf denen Personen relativ groß im Bild zu sehen sind. Aufgeteilt wurde der Datensatz in etwa 90 % Trainings- und 10 % Testdaten. Das Projektteam hat am Ende festgestellt, dass sich die Ergebnisse des „Validierungsskripts“ mit den Beobachtungen aus dem Systemtest widersprechen.

Grundsätzlich sind Tests wichtig, um die Erfüllung von Anforderungen anhand von korrektem Verhalten zu überprüfen. So auch für die Personenerkennung auf dem Fahrzeug. Aus dem Bericht [ACB+22] lässt sich bereits ein Testszenario entnehmen. Das „Testszenario zur Überprüfung der Teilprojektziele der Personenerkennung“ [ACB+22, Anhang G] des Berichts zeigt eine angepasste Version des „Testszenarios zur Überprüfung der Projektziele“ [ACB+22, Anhang F]. Die Version wurde aufgrund eines Zeitmangels bis zur Projektdeadline auf den damaligen Projektfortschritt angepasst. Entsprechend der Testszenarien wurde ein Systemtest durchgeführt, der mithilfe eines Videos festgehalten wurde (zu finden im Repository des WiSe 2021/22 unter *soc-nn\_main\_repo/abgabe/WiSe2122*) und einen Eindruck der Performance in einem Systemtest gibt. Ziel war es

das Testszenario auszuführen, im Video wurden jedoch nicht vollständig die Rahmenbedingungen des Szenarios eingehalten. Beispielsweise gibt es Zeitpunkte, zu denen zwei Personen im Bild zu sehen sind. Dort wurde die Personenerkennung auf dem Auto selbst mit der gesamten Hardware in der Praxis getestet. Im Projektbericht wird als Ergebnis von einer „subjektiven Einschätzung“ geschrieben, welche angibt, dass in mehr als 80 % der Fälle eine Person korrekt erkannt wird (vgl. [ACB+22, S. 35]). Die Methodik oder Grundlage dieser Einschätzung wird nicht genannt. Dieser Wert ist somit als nicht aussagekräftig zu bewerten und kann auch nicht reproduziert werden.

Als weiteren Test wurde zur Evaluation ein „Validierungsskript“ verwendet. Dieses prüft für einen Testdatensatz, wie viele Bilder von einem trainierten neuronalen Netz korrekt klassifiziert werden. Die Ausführung des Skripts findet in einer Python-Entwicklungsumgebung auf einem Rechner statt, Genaueres zum bisherigen Stand des Codes ist in [Abschnitt 3.4](#) aufgeführt. Für den verwendeten Datensatz gab das Skript eine Genauigkeit von etwa 50 % für das Modell an (vgl. [ACB+22, S. 27]). Allerdings ist dem Projektteam aufgefallen, dass das „Validierungsskript“ erhebliche Bugs aufwies, die im Wintersemester 2021/22 jedoch nicht mehr behoben wurden. Es wird davon ausgegangen, dass die schlechte Genauigkeit von 50 % und starke Abweichung vom Resultat des Systemtests auf das fehlerhafte Validierungsskript zurückzuführen sei.

Als Ausblick und mögliche Verbesserungen wird im Bericht aus dem Wintersemester 2021/22 genannt, dass die große Diskrepanz zwischen den ermittelten Werten der Genauigkeit des Modells untersucht werden soll, da eine aussagekräftige Evaluation essenziell für das Bewerten von Änderungen am Trainingsprozess ist. Weiterhin wird erwähnt, dass eine Überarbeitung des Trainingsskripts sinnvoll sein kann, da bisher nicht beim Training erkannt werden kann, wie viele Epochen optimalerweise trainiert werden sollte (vgl. [ACB+22, S. 39f.]).

### 3.4. Bisheriger Stand des Codes

Der gesamte Ablauf des Trainings- und Testverfahrens sowie der FINN Export geschehen in der Jupyter-Notebook-Datei `src/training/Train.ipynb` des `soc-nn_main_repo`. Dies wurde im Rahmen des Sommersemesters 2021 erarbeitet. Im Folgenden wird der gesamte Prozess beschrieben. Genaue Informationen zum Ablauf sind im Projektbericht des Sommersemesters 2021 [ACB+21, S. 107f.] nachzulesen. Der Code und die dortigen Erläuterungen sind zwar primär für die Gestenerkennung geschrieben, das Prinzip kann aber genauso auf die Personenerkennung angewendet werden, wie es auch bereits im Wintersemester 2021/22 getan wurde.

Das Jupyter Notebook ist in die Sektionen *Prepare Environment*, *Load Dataset*, *Show Class Ids*, *Training*, *Measure accuracy* und *FINN Export* aufgeteilt. Im ersten Teil werden die Pfade zu den Datensätzen angegeben und wo das Modell gespeichert bzw. abgerufen werden soll. Zudem werden die Konfigurationsparameter für das quantisierte neuronale Netz festgelegt und das Gerät bestimmt, auf dem das Training durchgeführt werden soll (Central Processing Unit (CPU) oder GPU). Unter *Load Dataset* wird der Datensatz erstellt. Dazu wird unter anderem die Batch Size bestimmt, die in diesem Fall 32 beträgt. Außerdem wird der Name des Datensatzes angegeben. Hier wird der COCO-Datensatz verwendet, der schon aufgeteilt in Trainings- und Testdaten vorliegt. Dementsprechend gibt es einen Ordner *train* und einen Ordner *test*, in denen es jeweils einen Ordner für die beiden Klassen *person* und *no person* gibt. Die Aufteilung zwischen Trainings- und Testdaten beträgt etwa 90/10. Im nächsten Schritt werden in der Konsole die aus dem Datensatz identifizierten Klassen ausgegeben.

Der Abschnitt *Training* beinhaltet das Training des neuronalen Netzes. Dazu wird das ausgelagerte

Trainingsskript (`src/training/trainers/basic.py`) verwendet. Zuerst wird eine Instanz der Klasse *Trainer* erstellt, die das neuronale Netz, den Pfad, wo die Gewichtungen gespeichert werden sollen, den Trainingsdatensatz, das „Trainingsgerät“ und die Anzahl der zu trainierenden Epochen übergeben bekommt. Anschließend wird die *train()*-Methode aufgerufen.

Das Testen des trainierten Modells erfolgt im anschließenden Abschnitt, ebenfalls mit einem ausgelagerten Skript. Hier gibt es die Klasse *Validator*, die das neuronale Netz, den Pfad zu den gespeicherten Gewichtungen, den Testdatensatz und auch das „Trainingsgerät“ übergeben bekommt. Um den Test auszuführen, wird die *validate()*-Methode aufgerufen. In dieser werden die Testdaten mithilfe des Modells klassifiziert, die vorhergesagten Labels mit den tatsächlichen verglichen und eine Genauigkeit des Modells bestimmt.

Unter dem Abschnitt *FINN Export* wird das trainierte, quantisierte Modell mit FINN, einem Framework für neuronale Netze auf FPGAs, so zu exportieren, dass es auf ein FPGA geladen werden kann. Nach erfolgreicher Ausführung des Trainings mit den festgelegten Python-Paket-Versionen (siehe Unterabschnitt 3.5.2) produzierte der FINN Export immer noch eine Vielzahl kryptischer Fehlermeldungen.

Der Code ist generell nicht einfach ausführbar, da weder die benötigten Python-Pakete noch ihre Versionen dokumentiert sind. Die einfache Installation der neusten Versionen aller im Code verwendeten Pakete führt zu Import-Fehlern, weil die installierten, neusten Versionen einiger Pakete nicht kompatibel mit den unbekannten, zuletzt verwendeten Versionen sind.

### 3.4.1. Bisheriger Stand und Probleme des Trainingsskripts

Das Trainingsskript trainiert ein Modell für eine vorgegebene Anzahl an Epochen. Dabei erfolgt keine Laufzeit-Überprüfung für Overfitting und anschließendes Early Stopping oder ähnliches. Das Modell, was aus der letzten Trainings-Epoche resultiert ist, wird gespeichert und als „bestes Modell“ weiter verwendet/getestet.

Das ist problematisch, da bei einer bestimmten (unbekannten) Anzahl an Trainings-Epochen das Modell anfängt zu overfitten, was nicht überprüft wird. Es sollte schon während des Trainings eine Validierung des Modells erfolgen, was (unter anderem) die Erkennung und Vermeidung von Overfitting erlaubt, aber auch ermöglicht, begründet das „beste Modell“ auszuwählen, anstatt blind das Letzte weiterzuverwenden.

### 3.4.2. Bisheriger Stand und Probleme des Testskripts

Das Testskript war zunächst nicht ausführbar, da die Variable *self.total* nicht definiert war, bevor sie das erste Mal ausgelesen wurde. Zudem wurde für jeden Batch das gesamte Modell des neuronalen Netzes neu geladen, was unnötig Rechenzeit beansprucht. Ein weiteres Problem war, dass die Batch Size nicht richtig bestimmt wurde. Dadurch sind immer nur zwei Bilder statt 32 pro Batch überprüft worden. Dementsprechend wurde nur ein kleiner Teil der Testdaten wirklich verwendet. Außerdem waren auch die Textausgabe und das Plotting der Bilder fehlerhaft. Dies ist in Unterabschnitt 3.4.3 genauer aufgezeigt.

### 3.4.3. Durchführen des Trainings- und Testverfahrens mit bestehendem Modell und Skript

Um den aktuellen Stand und die bisherigen Ergebnisse besser beurteilen zu können, wurde das gesamte Trainings- und Testverfahren mit den bestehenden Skripten durchgeführt. Dazu waren zunächst einige Änderungen notwendig, damit die Skripte ausführbar waren und eine beurteilbare Ausgabe lieferten. Diese Änderungen wurden in den Dateien `src/training/validators/basic.py` und `src/training/Train.ipynb` des `soc-nn_main_repo` vorgenommen. Erstere enthält das Testskript und musste dahingehend angepasst werden, dass die Variable `self.total` am Anfang initialisiert werden musste. Im Jupyter Notebook mussten die Pfade an die eigene Dateistruktur angepasst werden. Zudem war eine Namensänderung des Datensatzes nötig. Für die richtige Ausgabe der Ergebnisse wurde beim Training `print_every` auf 10 gesetzt, damit es während des Trainings Statusupdates gibt. Außerdem wurde `print_test_information` auf `True` gesetzt, um einen ausführlichen Output der Testergebnisse zu ermöglichen. Der FINN-Export bleibt unverändert und damit nicht funktionsfähig, da er das Ziel unserer Aufgabenstellung nicht relevant ist. Der Code, mit dem das Training- und Testverfahren durchgeführt wurde, befindet sich in einer separat exportierten zip im Repository `baseline-running-version.zip`. Wie dort auch in der README beschrieben, wurde der Datensatz selbst nicht exportiert. Es wurde jedoch der gleiche Datensatz, wie in der finalen Version auf dem Repo, verwendet.

Bei einer Durchführung des alten Testskripts nach Trainieren eines Modells über 10 Epochen lieferte das Skript folgende Ergebnisse. Von den eigentlich knapp 160 Testbildern wurden letztendlich nur 10 getestet. Davon wurden 6 Bilder falsch vom Modell klassifiziert, was einer unbrauchbaren Accuracy von 40 % entspricht. Auf unterschiedlichen Geräten wurden mit gleichem Code zudem unterschiedliche Werte ermittelt (40 %, 50 % und 70 %), was untermauert, dass das „Validierungsskript“ unbrauchbar ist. Außerdem gibt es allgemein Fehler in der Ausgabe der Ergebnisse. Diese sind in [Abbildung 3.1](#) zu erkennen. Zum einen kommen in der Textausgabe Bilder mehrfach vor, gleiche Bilder werden teilweise unterschiedlich klassifiziert laut dem Output und Label und Prediction stimmen teilweise überein, obwohl die jeweiligen Bilder angeblich falsch klassifiziert wurden. Auch die Ausgabe der Bilder weist erhebliche Fehler auf. Die Bilder passen nicht zu den angegebenen Pfaden, da alle Bilder eine Person zeigen, obwohl in allen Pfaden „noperson“ steht.

```

Executed at 2025.06.26 23:36:07 in 3s 306ms

image noperson/00000000285.jpg - wrong | predicted: person

image noperson/00000000632.jpg - wrong | predicted: person

image noperson/00000000285.jpg - wrong | predicted: person

image noperson/00000000285.jpg - wrong | predicted: noperson

image noperson/00000000285.jpg - wrong | predicted: noperson

image noperson/00000000632.jpg - wrong | predicted: noperson

10 images. 6 were predicted wrong. Accuracy: 40.0%

noperson/00000000285.jpg

noperson/00000000632.jpg

noperson/00000000724.jpg

noperson/00000000776.jpg

noperson/00000000802.jpg

noperson/00000001425.jpg

noperson/00000001503.jpg

noperson/00000001532.jpg

noperson/00000001675.jpg

noperson/00000001818.jpg

```

Abbildung 3.1.: Fehlerhafter Output des Validierungsskriptes; Lizenz Personenbilder: CC BY 4.0 [Cre]

## 3.5. Verbesserungen

### 3.5.1. Allgemeine Verbesserungen

In vorgänger Projekten wurde auf ein Cloud-Training zurückgegriffen. Die Einrichtung und der nötige Import und Export für jeden Trainingsdurchlauf wurde als großer Nachteil und zusätzlicher Aufwand gesehen. Die Vorteile für eine einheitliche Umgebung konnten mit Verbesserungen für eine reproduzierbare Entwicklungsumgebung erreicht werden und ein schnelles Training konnte durch die Verwendung einer GPU (siehe Unterabschnitt 3.5.3) erreicht werden. Aus diesen Gründen wird das Training lokal und nicht in der Cloud ausgeführt, womit eine deutliche schnellere Entwicklung und Verbesserung der Skripte möglich ist.

Bei der initialen Erstellung des Trainingsprozesses in [ACB+21] wurde Beispielcode für das ausgewählte Model *CNV* von Brevitas [FPF25] übernommen (vgl. [ACB+21, S. 55]). Dies wurde zwar im Bericht dokumentiert, aber im Code nicht angegeben. Der Code in den entsprechenden drei Dateien (*src/models/cnv.py*, *src/models/common.py* und *src/models/tensor\_norm.py*) wurde in diesem Jahr auf den aktuellsten Beispielcode von Brevitas aktualisiert. Dabei wurde die Originalquelle<sup>1</sup>, die Lizenz und jegliche Änderungen im Code angegeben. Der Code ist unter der „3-Clause BSD“ Lizenz [Reg] verfügbar. Nicht verwendeter Beispielcode wurde entfernt.

Die bisherige Aufteilung in Trainings- und Testdaten wurde in einen *Train-Validate-Test-Split*

<sup>1</sup>[https://github.com/Xilinx/brevitas/blob/41b78bbee5c3d5b7514906048c19ebd766339b53/src/brevitas\\_examp.../bnn\\_pynq/models/](https://github.com/Xilinx/brevitas/blob/41b78bbee5c3d5b7514906048c19ebd766339b53/src/brevitas_examp.../bnn_pynq/models/)

geändert. Somit besteht nun die Möglichkeit, einen Validierungsdatensatz zur Vermeidung von Overfitting zu verwenden. Die Daten liegen zunächst weiterhin in der bisherigen Aufteilung vor. Vor dem Training wird zusätzlich der Trainingsdatensatz in *Train* und *Validate* aufgeteilt. Dazu wurde der Parameter *validate\_ratio* eingeführt, um das Verhältnis zu bestimmen. In diesem Fall wurde sich für eine 80/20-Aufteilung entschieden.

In diesem Zuge ist auch aufgefallen, dass das „Validierungsskript“ eigentlich ein Testskript ist. Die Überprüfung der Accuracy nach dem abgeschlossenen Training wird als Test bezeichnet, während die Validierung in jeder Epoche des Trainings zur Bestimmung des Validation Losses stattfindet. Daher wurde die Klasse *Validator* in *Tester* umbenannt und entsprechend auch weitere notwendige Namensänderungen durchgeführt.

Des Weiteren wurde im Teil *Prepare Environment* des Jupyter Notebooks der Parameter *num\_classes* von 3 auf 2 gesetzt, da bei der Personenerkennung nur die Klassen PERSON und NOPERSON existieren. Zuvor wurde bei der Gestenerkennung zwischen 3 Klassen unterschieden.

Zuletzt wurde versucht, Determinismus für das Trainings-Notebook zu konfigurieren, was aus unbekannten Gründen nicht erfolgreich war. Alle verwendeten Python-Pakete, die es unterstützen, wurden entsprechend konfiguriert (z. B. durch die Angabe eines festen Seeds für Zufalls-Operationen), jedoch ist trotzdem ein nicht-determinismus des Codes feststellbar, z. B. durch unterschiedlich gute Modelle die nach dem Training mit dem selben Code auf dem selben Gerät entstehen.

### 3.5.2. Verbesserungen für eine reproduzierbare Entwicklungsumgebung

Da bei den meisten verwendeten Python-Paketen nicht bekannt war, welche Version zuletzt verwendet wurde, wurde nun initial von der jeweils neusten Version ausgegangen, mit der Vermutung, dass für einige Packages ältere Versionen benötigt werden. Bis auf *dependencies* (für Dependency Injection) und *brevitas* (für quantisierte neuronale Netze) haben die aktuell neusten Paket-Versionen problemlos funktioniert.

Bezüglich Brevitas war aus vorheriger Projektdokumentation bekannt, dass zuletzt die Version 0.2.0a (Alpha, Januar 2021) eingesetzt wurde. Diese Version war erforderlich, da der benötigte FINN-ONNX-Export in späteren Versionen verändert, und schließlich in Version v0.10.0 (Dezember 2023)<sup>2</sup> in seiner bisherigen Form sogar ganz entfernt wurde. Die Installation der Alpha-Version gestaltete sich jedoch problematisch, da sie lokal aus dem Quellcode gebaut werden musste, was aus unklaren Gründen nur auf einem unserer Geräte erfolgreich war.

Mit der nächst-besten Version (0.2.0), die in dem offiziellen Python Package Repository PyPI verfügbar war, traten wiederholt Probleme beim Import des FINN-ONNX-Exporters auf, die teils nur durch einen Neustart der Entwicklungsumgebung behoben werden konnten.

Als Nächstes wurde die Version 0.9.1 (April 2023) untersucht, da sie die neuste Version ist, die den FINN-ONNX-Export noch enthält. Nach kleinen Anpassungen an veränderte Funktionsnamen und Modul-Strukturen dieser Brevitas-Version lief sie auf allen getesteten Geräten stabil und ohne Fehler. Auch musste der Input-Shape der *INTERMEDIATE\_FC\_FEATURES* in *src/models/cnv.py* im Modell angepasst werden, dort scheint sich das Verhalten von Brevitas auch verändert zu haben. Des Weiteren zeigte sich, dass die Brevitas-Versionen 0.2.0a bis (mindestens) 0.9.1 mit Python-Versionen größer als 3.12 inkompatibel sind, was zu Fehlern führte. Erfolgreichere Tests wurden mit Python 3.11.7 und 3.12.10 durchgeführt.

---

<sup>2</sup> „Deprecated FINN ONNX export flow.“ <https://github.com/Xilinx/brevitas/releases/tag/v0.10.0>

Die benötigte dependencies-Paket-Version war abhängig von Brevitas und wurde auf 2.0.1 (Juli 2020) festgesetzt.

Diese bestimmten Python-Paket-Versionen, mit denen der Code nun garantiert ausführbar ist, wurden in einer Python-typischen `requirements.txt`-Datei festgehalten, womit in Zukunft reproduzierbar die richtigen Versionen installiert und damit der Code ausgeführt werden können. Spezifisch für die Ausführung des Codes auf der Linux-Distribution NixOS liegt nun im Repository auch eine `flake.nix`<sup>3</sup> für eine reproduzierbare Entwicklungsumgebung bei.

### 3.5.3. Trainingsskript Verbesserung

Die unter Abschnitt [Abschnitt 3.4](#) aufgeführten Probleme wurden behoben und das Training generell optimiert. Dabei wurden Bezeichner klarer benannt, der Code modularer gestaltet und aufgeräumt, sowie Dokumentationskommentare ergänzt.

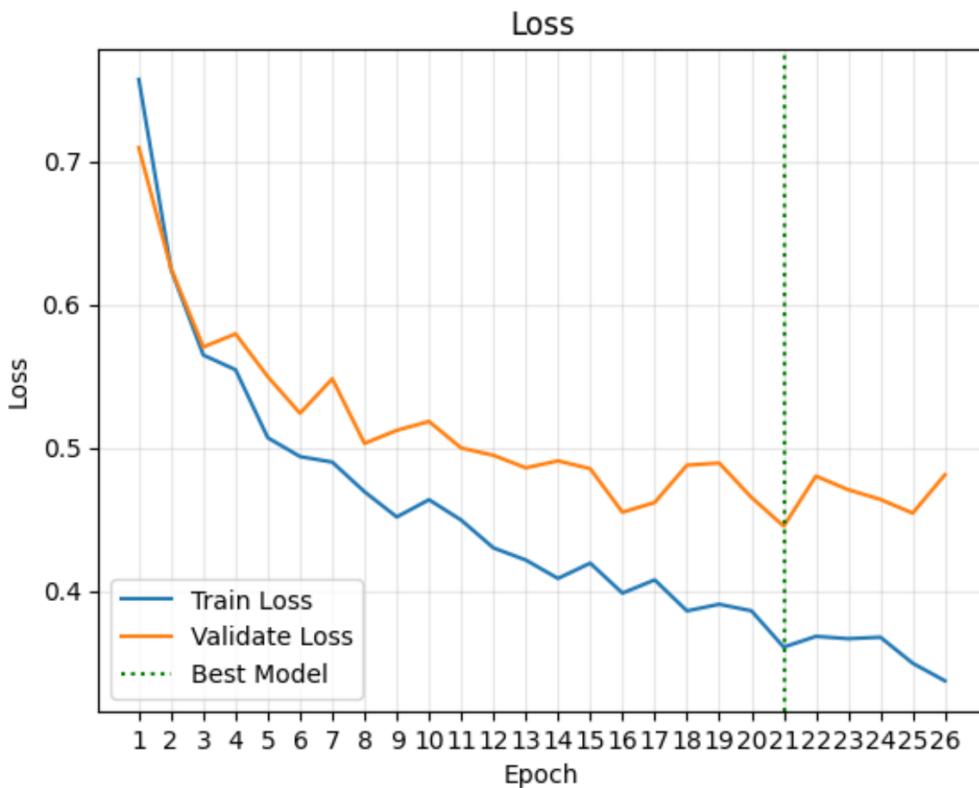

Zuerst wird das Trainingsskript, wie in [Listing 3.1](#) abgebildet, angepasst, dass Overfitting (Definition siehe [Unterabschnitt 3.2.1](#)) des Modells weitestgehend vermieden werden kann. Dazu wird nach jeder Trainingsepoch das Modell mit von den Trainingsdaten unabhängigen Validierungsdaten validiert und ein *Loss* berechnet. Verbessert sich dieser über eine bestimmte Anzahl an Epochen nicht, wird das Training abgebrochen („Early Stopping“).

Listing 3.1: Verbesserung: Overfitting vermeiden

```

1 # if model improved

2 if mean_validate_loss < best_validate_loss:

3     best_validate_loss = mean_validate_loss

4     epochs_without_improvement = 0

5     self.history["best_epoch"] = epoch+1

6     if best_validate_loss < previous_model_best_val_loss:

7         # save model only if its better than the last saved model

8         overwritten_prev_best_model = True

9         self.save_best(epoch, best_validate_loss)

10 else:

11     epochs_without_improvement += 1

12     if epochs_without_improvement >= self.patience:

13         print(f"Early stopping after epoch {epoch+1}, validate loss did

14             not improve for {epochs_without_improvement} epochs")

15         break

```

Zudem wird das Modell mit der `save_best()` Methode jedes Mal gespeichert, wenn ein neues bestes Modell (niedrigster Validierungs-Loss) gefunden wurde. Es wird darüber hinaus auch nur ein neues Modell gespeichert, wenn dieses einen niedrigeren Validation-Loss als ein vorher trainiertes aufweist. Somit wird vermieden, dass ein Modell welches im Training ein lokalen Optimum darstellt, nicht das bessere Modell (möglicherweise globales Optimum) überschreibt.

Zudem wurde der Datensatz mit der Methode des Stratified Sampling (vgl. [3.2.2](#)) aufgeteilt, wie in Tabelle [3.1](#) dargestellt. Es ist zu erkennen, dass so die Klassenverhältnisse nahezu gleich sind und damit reproduzierbare und unverzerrte Trainings, Tests und Validierungen sicherstellen.

<sup>3</sup>Flakes sind ein experimentelles-Feature von NixOS (siehe <https://wiki.nixos.org/wiki/Flakes>)

| Label    | Trainings-Samples | Validierungs-Samples | Test-Samples |

|----------|-------------------|----------------------|--------------|

| person   | 566               | 142                  | 79           |

| noperson | 566               | 142                  | 78           |

Tabelle 3.1.: Aufteilung des Datensatzes in Trainings-, Validierungs- und Testdaten

Für den Trainingsprozess wurde die Konsolenausgabe verbessert und eine Visualisierung des Train- und Validate-Losses über den Verlauf des Trainings hinzugefügt.

```

[Epoch 25] Average loss over last 10 Batches: 0.378

[Epoch 25] Average loss over last 20 Batches: 0.379

[Epoch 25] Average loss over last 30 Batches: 0.370

[Epoch 26] Average loss over last 10 Batches: 0.366

[Epoch 26] Average loss over last 20 Batches: 0.342

[Epoch 26] Average loss over last 30 Batches: 0.354

Early stopping after epoch 26, validate loss did not improve for 5 epochs

Finished Training in 14.382s.

```

```

No new best model found, the previous best model is still the best one with validate loss: 0.445

```

Abbildung 3.2.: Ausschnitt des Konsolenoutputs bezüglich des Trainierens des Modells

Abbildung 3.3.: Plotting des Verlaufs von Train Loss und Validate Loss

Wie bereits erwähnt (siehe [Abschnitt 3.3](#)) konnte das Training in vorherigen Projekten nicht auf einer GPU ausgeführt werden. Der Code wurde nun mit Nvidia CUDA [NVla] kompatibel gemacht. Dies ermöglicht es, dass das Training auf leistungsfähigen und massiv parallelisierbaren Nvidia-Grafikkarten-Chips laufen kann und die Trainingszeit deutlich reduziert. Die dafür nötigen

Voraussetzungen und weiterführende Ressourcen können im [Abschnitt F.1](#) eingesehen werden. In dem in [Tabelle 3.2](#) dargestellten Vergleich wird deutlich, wie hoch der Performanzgewinn ist <sup>4</sup> <sub>5</sub>. Dabei wird das Training 5 mal mit maximal 100 Epochen durchgeführt, und die durchschnittliche Performanz dieser Trainings betrachtet. Die Tabelle der Einzelzeiten kann im [Anhang F](#) eingesehen werden.

| Hardware            | Durchschnittliche Trainingszeit in s |

|---------------------|--------------------------------------|

| CPU                 | 426.526                              |

| Nvidia Grafikkarten | 13.3408                              |

Tabelle 3.2.: Durchschnittliche Trainingszeiten auf verschiedener Hardware

Im Fall der konkreten verwendeten Hardware bietet die dedizierte Grafikkarte eine nahezu 32-fache Verbesserung der Laufzeit gegenüber der [CPU](#).

### 3.5.4. Testskript Verbesserung

Die Probleme des Testskripts, die in [3.4](#) beschrieben sind, wurden gelöst. Zudem wurde der Code und die Codestruktur allgemein verbessert. Die konkreten Umsetzungen werden im Folgenden erklärt.

Um die Performance des Skripts zu verbessern, wird das trainierte Modell jetzt einmal initial geladen. Weiterhin ist eine Konsolenausgabe hinzugefügt worden, um den Nutzer darüber zu informieren, dass das Modell erfolgreich geladen wurde und aus welcher Epoche das Modell stammt. Diese Ausgabe ist in [Abbildung 3.4](#) zu sehen.

```

Loaded best model (from epoch 21)

157 images. 74 were predicted wrong. Accuracy: 52.86624203821656%

```

Abbildung 3.4.: Ausgabe des Ladens und der Accuracy des Modells

Außerdem wird nun die Größe des Batches richtig bestimmt, sodass korrekt über alle Bilder eines Batches iteriert wird. Somit werden nun alle Bilder des Testdatensatzes auch wirklich getestet. Dies resultiert in einer Accuracy von etwa  $\approx 53\%$  (siehe [Abbildung 3.4](#)). Dieser Wert ist nicht zufriedenstellend. Geht man davon aus, dass das Testskript nun die korrekte Accuracy liefert, müssen Training und/oder Testdaten geändert werden, um die Genauigkeit des Modells zu verbessern. Durch die Anpassungen am Testskript konnte die Accuracy nur minimal verbessert werden, wodurch die anfängliche Vermutung zu widerlegen ist, dass der schlechte Wert, der im Wintersemester 2021/22 ermittelt wurde, ausschließlich auf die Bugs und Fehler im ehemals Validierungsskript zurückzuführen sind.

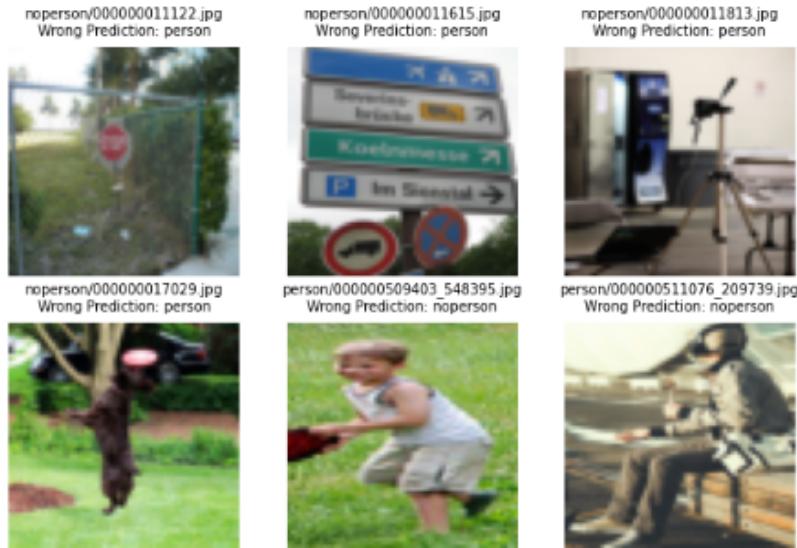

Um nicht die gesamten Testbilder zu plotten, wurde das Testskript dahingehend geändert, dass nur noch die falsch klassifizierten Bilder ausgegeben werden. Diese werden mit dem Dateipfad und der Vorhersage versehen (siehe [Abbildung 3.5](#)) und die Größe des Plots anhand der Anzahl

<sup>4</sup>Es wurde ein 11th Gen Intel(R) Core(TM) i7-11850H (16) @ 2.50 GHz repräsentativ für das Training auf einer CPU verwendet

<sup>5</sup>Es wurde eine Nvidia RTX 4080 mit 9728 CUDA Kernen repräsentativ für das Training auf einer Grafikkarte verwendet

der zu plottenden Bilder ermittelt. Des Weiteren wurde der detaillierte Textoutput der falsch klassifizierten Bilder entfernt, da dieser keine zusätzlichen Informationen enthält.

Abbildung 3.5.: Ausschnitt der ausgegebenen falsch klassifizierten Bilder; Lizenz Personenbilder: CC BY 4.0 [Cre]

Da die Accuracy allein nicht aussagekräftig genug ist, um das Testen gut bewerten zu können, wurde der Output um eine Konfusionsmatrix und den MCC erweitert. Dies ist in Abbildung 3.6 dargestellt. Der MCC kann in einem Intervall von -1 (schlecht) bis 1 (gut) liegen. Ein Wert von  $\approx 0,1$  bedeutet dabei, dass das Modell ähnlich akkurat ist wie ein Münzwurf, was nicht zufriedenstellend ist. Auch die Konfusionsmatrix zeigt, dass die Vorhersagen nur unwesentlich häufiger richtig als falsch sind.

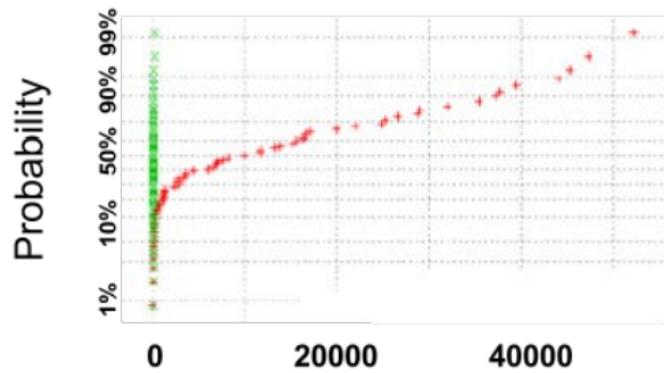

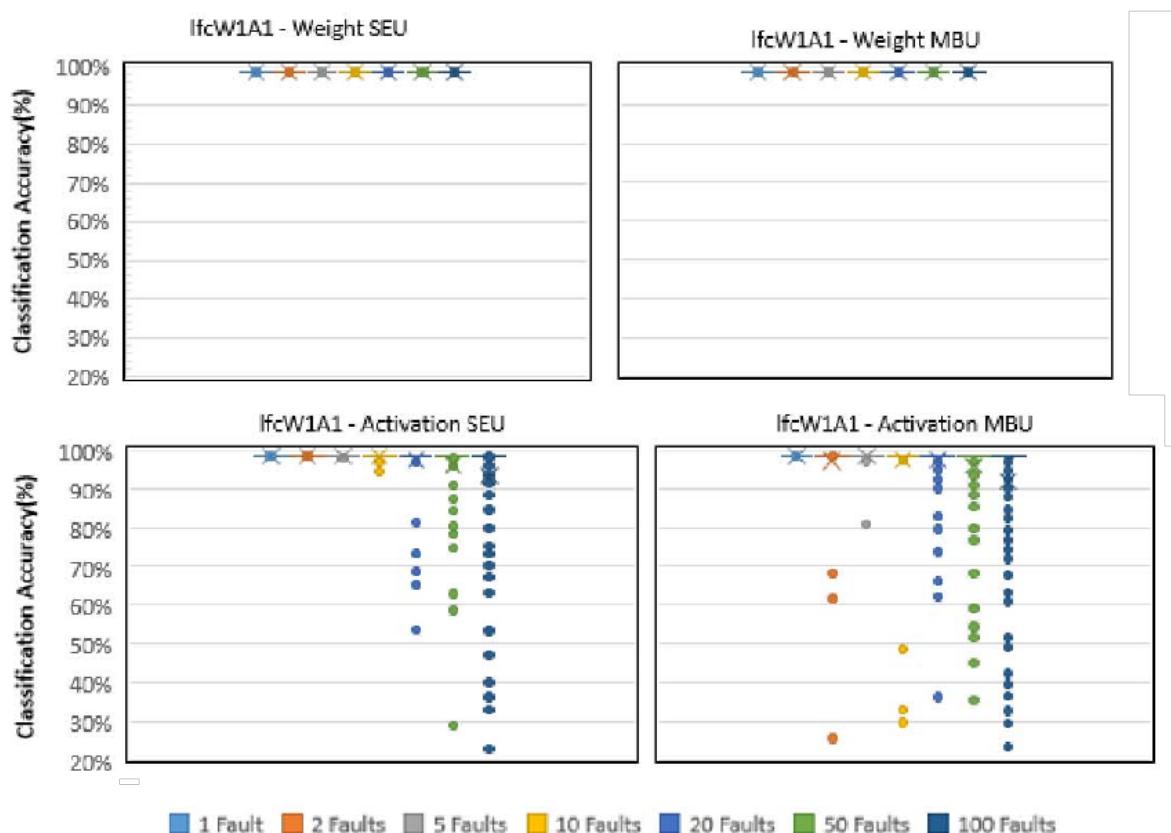

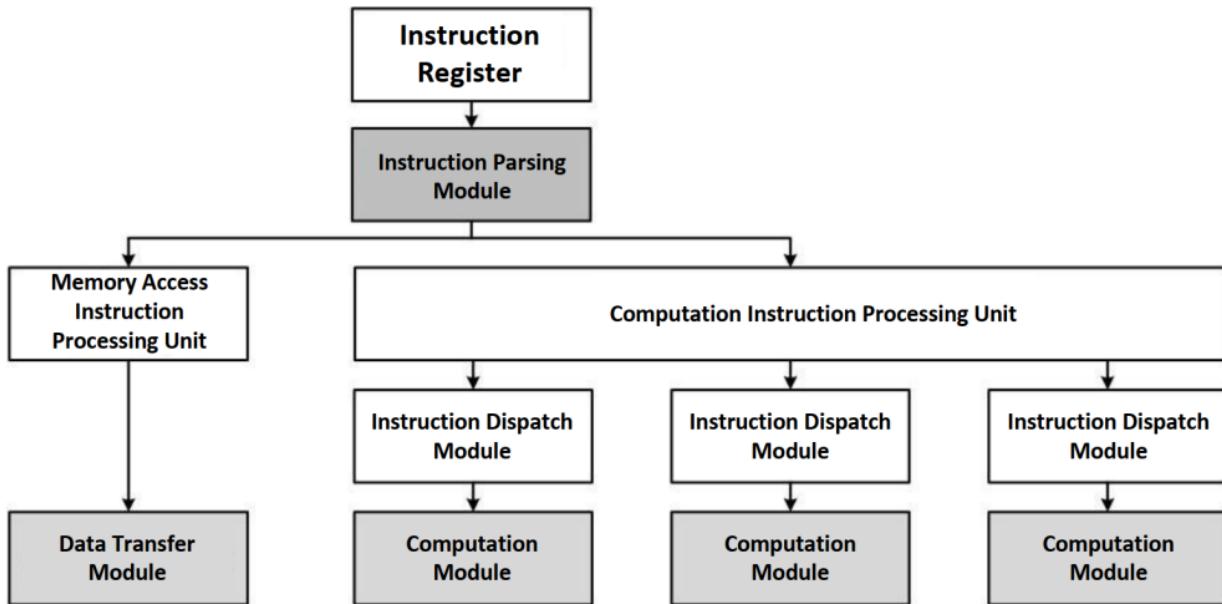

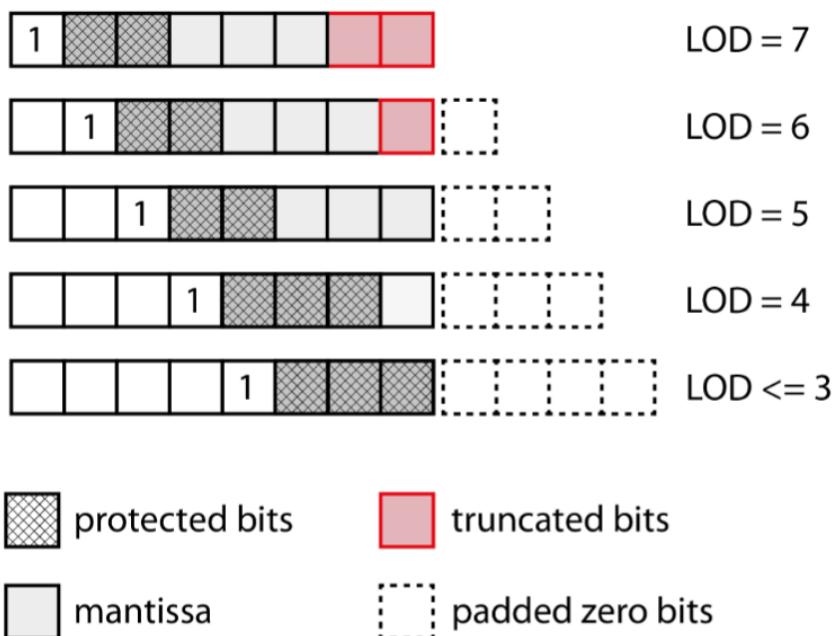

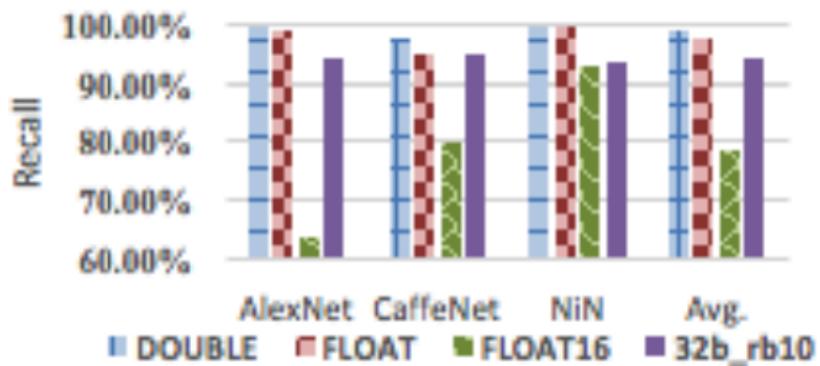

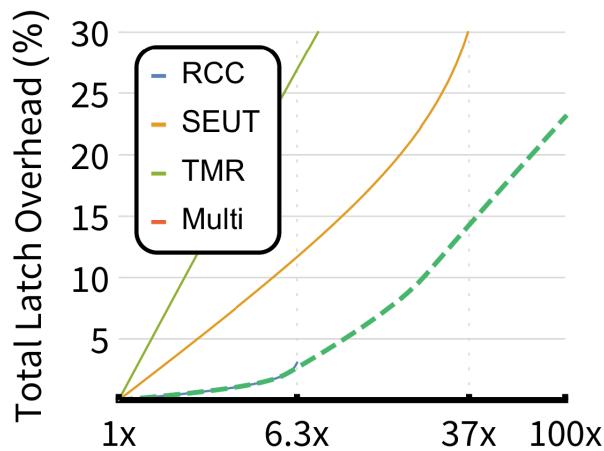

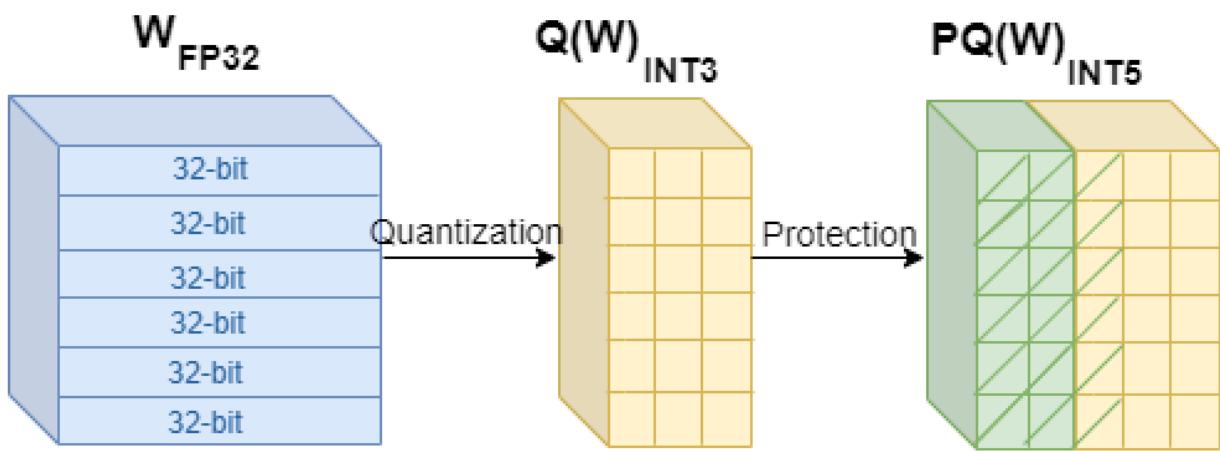

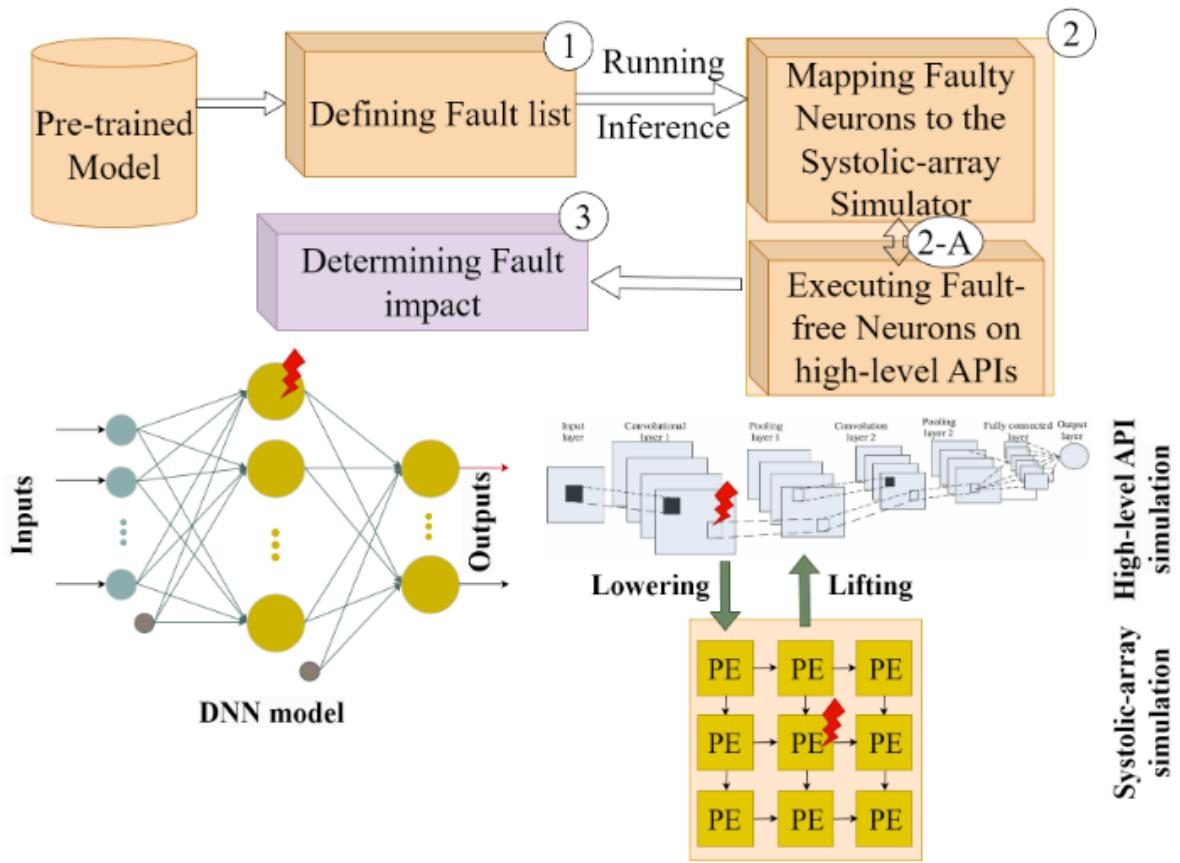

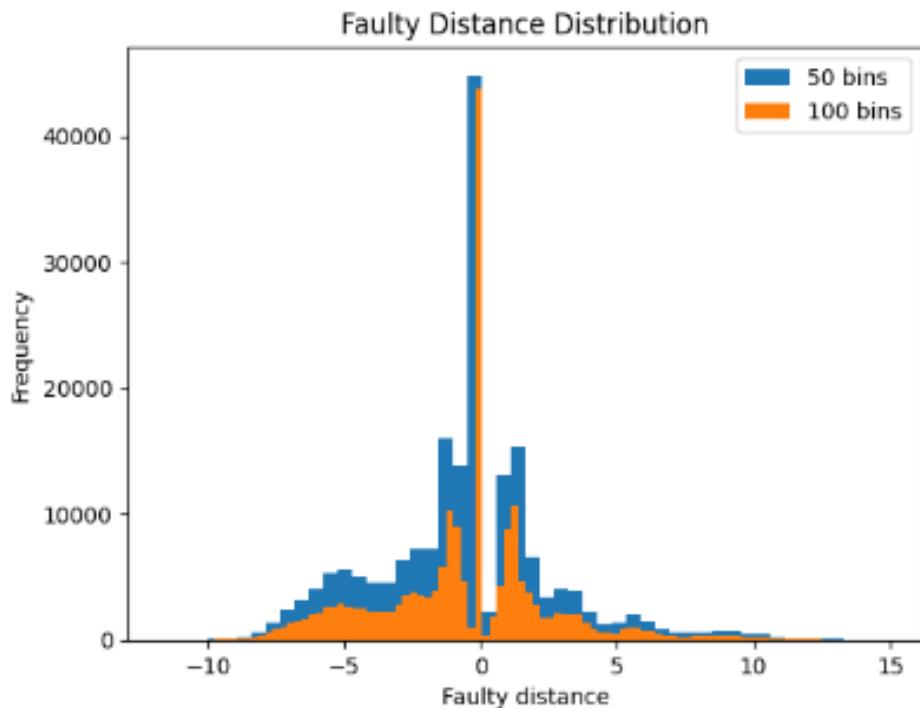

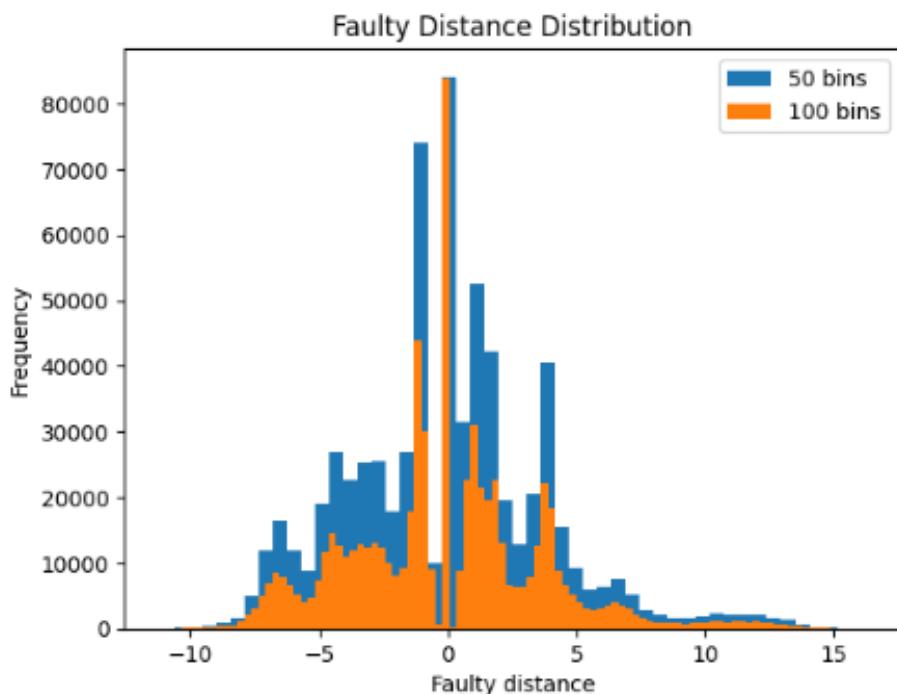

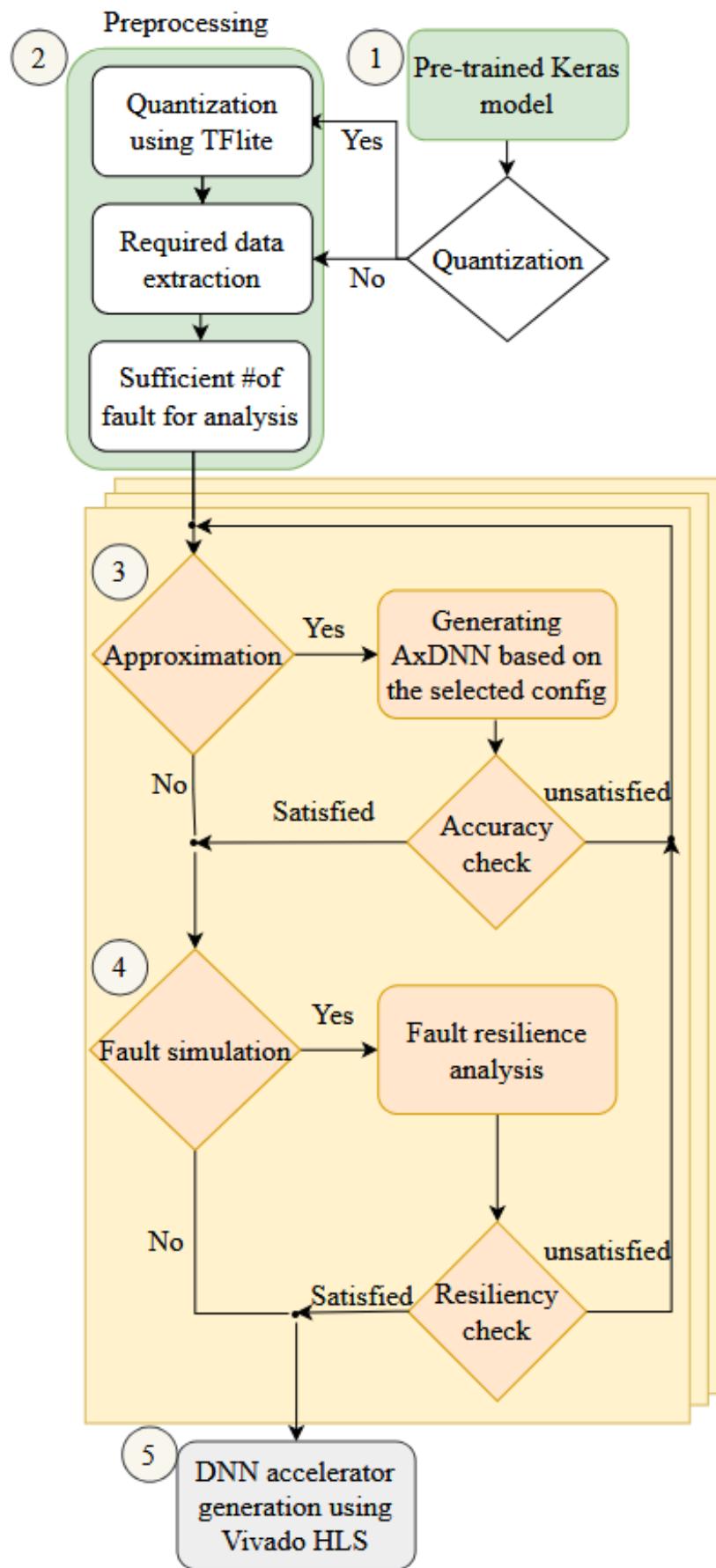

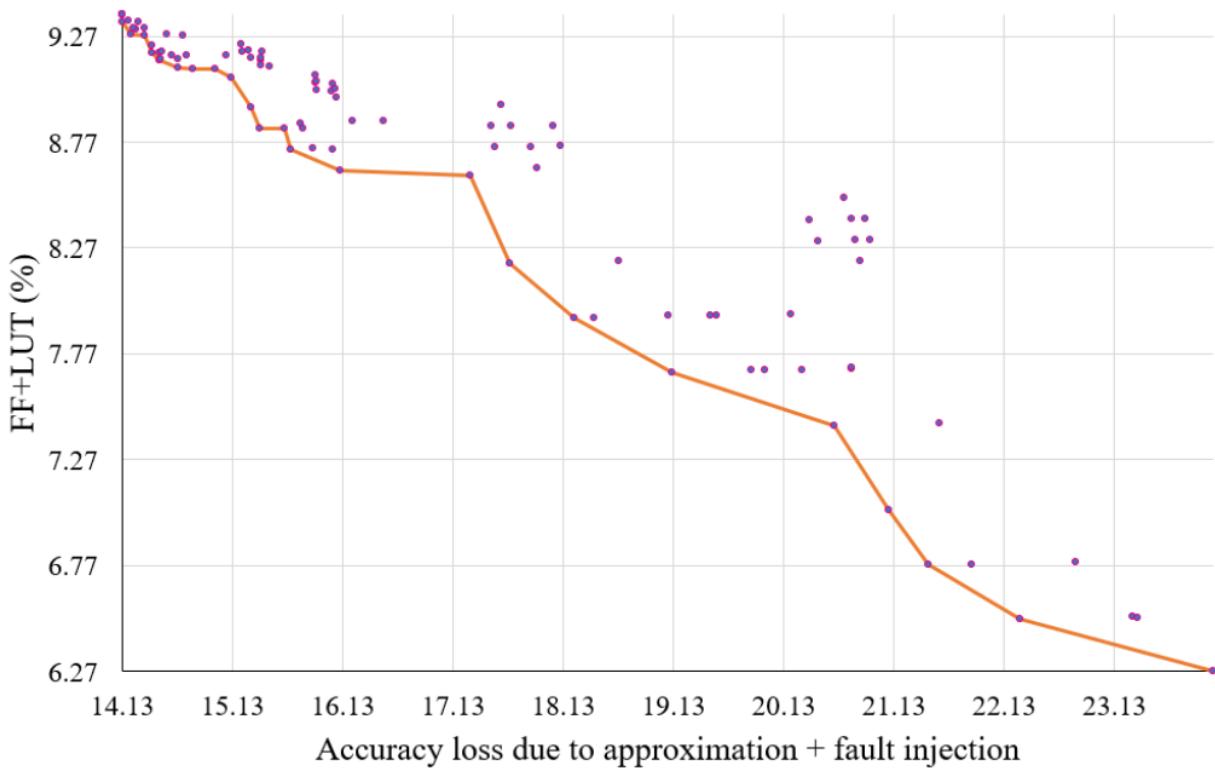

Abbildung 3.6.: Konfusionsmatrix